96

ABOV Semiconductor Co., Ltd.

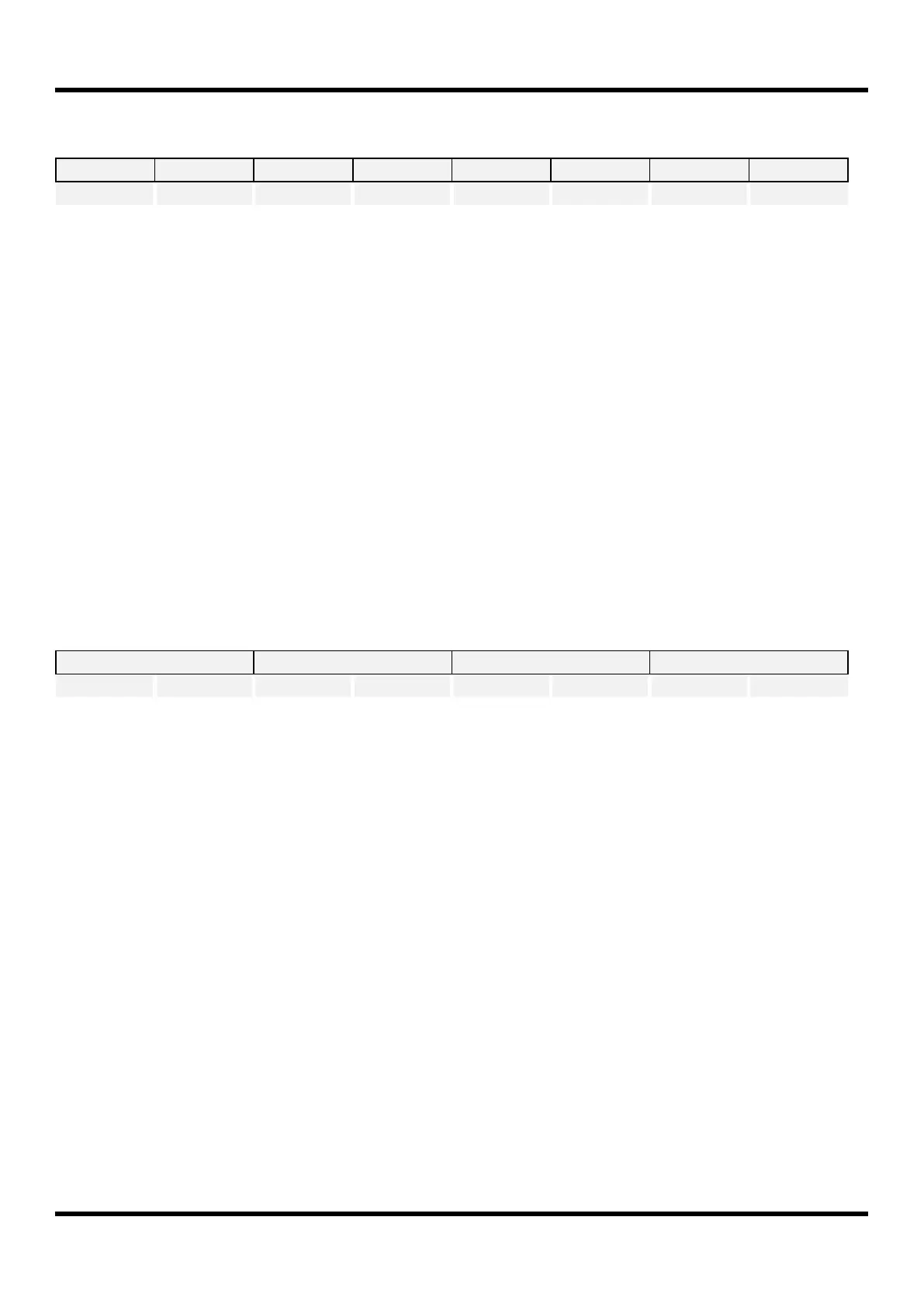

EIFLAG1 (External Interrupt Flag 1 Register): A6H

Initial value :00H

When T0 overflow interrupt occurs, this bit becomes ‘1’. For clearing bit, write‘0’ to

this bit or automatically clear by INT_ACK signal. Writing “1” has no effect.

T0 overflow Interrupt no generation

T0 overflow Interrupt generation

When T0 interrupt occurs, this bit becomes ‘1’. For clearing bit, write ‘0’ to this bit or

automatically clear by INT_ACK signal. Writing “1” has no effect.

T0 Interrupt no generation

When T3 interrupt occurs, this bit becomes ‘1’. For clearing bit, write ‘0’ to this bit or

automatically clear by INT_ACK signal. Writing “1” has no effect.

T3 Interrupt no generation

When an External Interrupt (EINT8, EINT10-EINT12) is occurred, the flag becomes

‘1’. The flag is cleared by writing ‘0’ to the bit or automatically cleared by INT_ACK

signal. Writing “1” has no effect.

External Interrupt not occurred

External Interrupt occurred

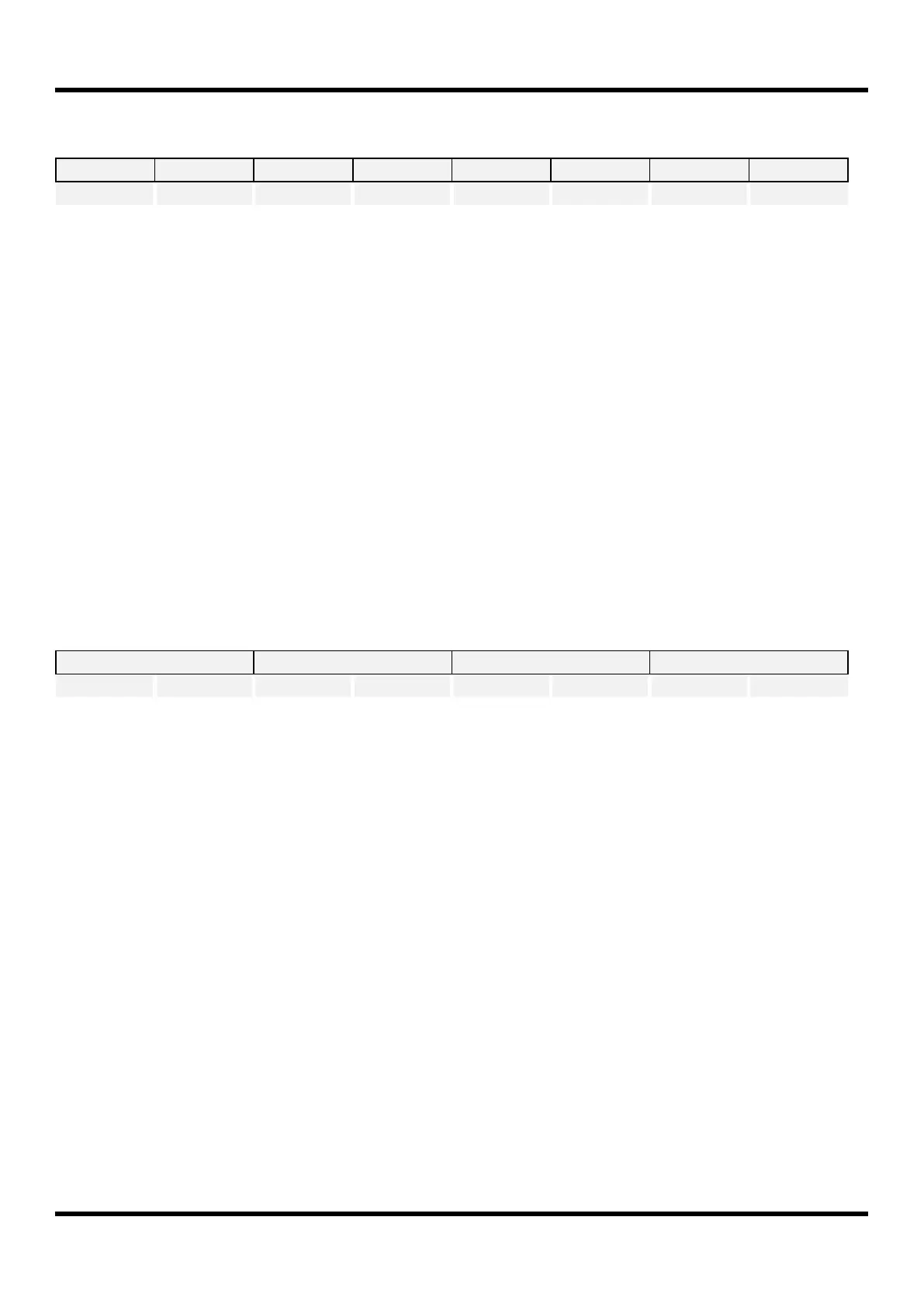

EIPOL1 (External Interrupt Polarity 1 Register): A7H

Initial value: 00H

External interrupt (EINT8,EINT10,EINT11,EINT12) polarity selection

Interrupt on falling edge

Interrupt on both of rising and falling edge

Where n =8, 10, 11 and 12

Loading...

Loading...