Table 4-6 SCC_DLL Register bit assignments (continued)

Bits Name Function

[15:1] - Reserved. Do not write to these bits.

[0] ALL_UNMASKED_DLLS_LOCKED This bit indicates whether or not all unmasked DLLs are locked:

• 0b0 One or more unmasked DLLs are not locked.

• 0b1 All unmasked DLLs are locked.

Related information

4.3 Register summary on page 4-62

4.4.7 SCC_AID Register

The SCC_AID Register characteristics are:

Purpose

The SCC_AID Register contains the FPGA build number, the target board of the FPGA build,

and information about the SCC register implementation.

Usage constraints

The SCC_AID Register is read-only.

Configurations

Available in all MPS2 and MPS2+ configurations.

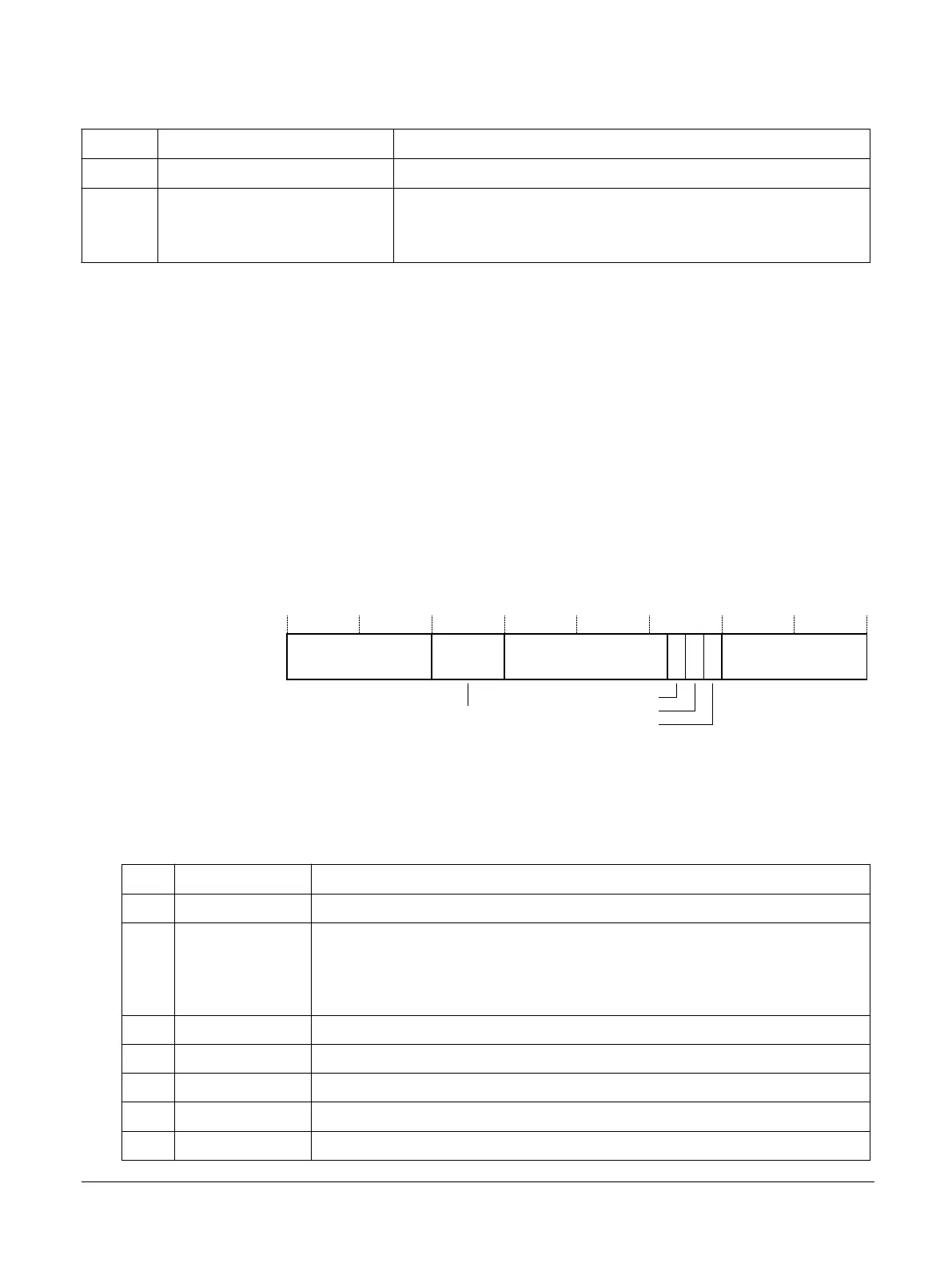

The following figure shows the bit assignments.

31

0

Reserved

CFGREGNUM

7824 23 11 10 9

SW_ENABLE

LED_ENABLE

LOCK_ENABLE

FPGA build

Target

board

revision

20 19

Figure 4-6 SCC_AID Register bit assignments

The following table shows the bit assignments.

Table 4-7 SCC_AID Register bit assignments

Bits Name Function

[31:24] Build FPGA build number.

[23:20] Target board revision. These bits indicate the target board revision of the FPGA build.

• 0000 = A

• 0001 = B

• 0010 = C

[19:11] - Reserved. Do not write to these bits.

[10] SW_ENABLE This bit indicates whether the system supports the SCC_SW_READ command.

[9] LED_ENABLE This bit indicates whether the system supports the SCC_LED_READ command.

[8] LOCK_ENABLE This bit indicates whether the system supports the SCC_LOCK_READ command.

[7:0] CFGREGNUM These bits indicate the number of user registers you can define. The maximum number is eight.

4 Programmers Model

4.4 SCC register descriptions

100112_0200_09_en Copyright © 2013–2016, 2018–2020 Arm Limited or its affiliates. All

rights reserved.

4-67

Non-Confidential

Loading...

Loading...