DL205 User Manual, 4th Edition, Rev. B

5–213

Chapter 5: Standard RLL Instructions - ASCII

1

2

3

4

5

6

7

8

9

10

11

12

13

14

A

B

C

D

AIN Fixed Length Configuration

• Length Type: select fixed length based on the length of the ASCII string that will be sent to the

CPU port

• Port Number: must be DL260 port 2 (K2)

• Data Destination: specifies where the ASCII string will be placed in V–memory

• Fixed Length: specifies the length, in bytes, of the fixed length ASCII string the port will receive

• Inter–character Timeout: if the amount of time between incoming ASCII characters exceeds the set

time, the specified Timeout Error bit will be set. No data will be stored at the Data Destination

V–memory location. The bit will reset when the AIN instruction permissive bits are disabled. None

selection disables this feature.

• First Character Timeout: if the amount of time from when the AIN is enabled to the time the first

character is received exceeds the set time, the specified First Character Timeout bit will be set. The

bit will reset when the AIN instruction permissive bits are disabled. None selection disables this

feature.

• Byte Swap: swaps the high–byte and low–byte within each V–memory register of the Fixed Length

ASCII string. See the SWAPB instruction for details.

• Busy Bit: is ON while the AIN instruction is receiving ASCII data

• Complete Bit: is set once the ASCII data has been received for the specified fixed length and reset

when the AIN instruction permissive bits are disabled.

• Inter–character Timeout Error Bit: is set when the Character Timeout is exceed. See Character

Timeout explanation above.

• First Character Timeout Error Bit: is set when the First Character Timeout is exceed. See First

Character Timeout explanation above.

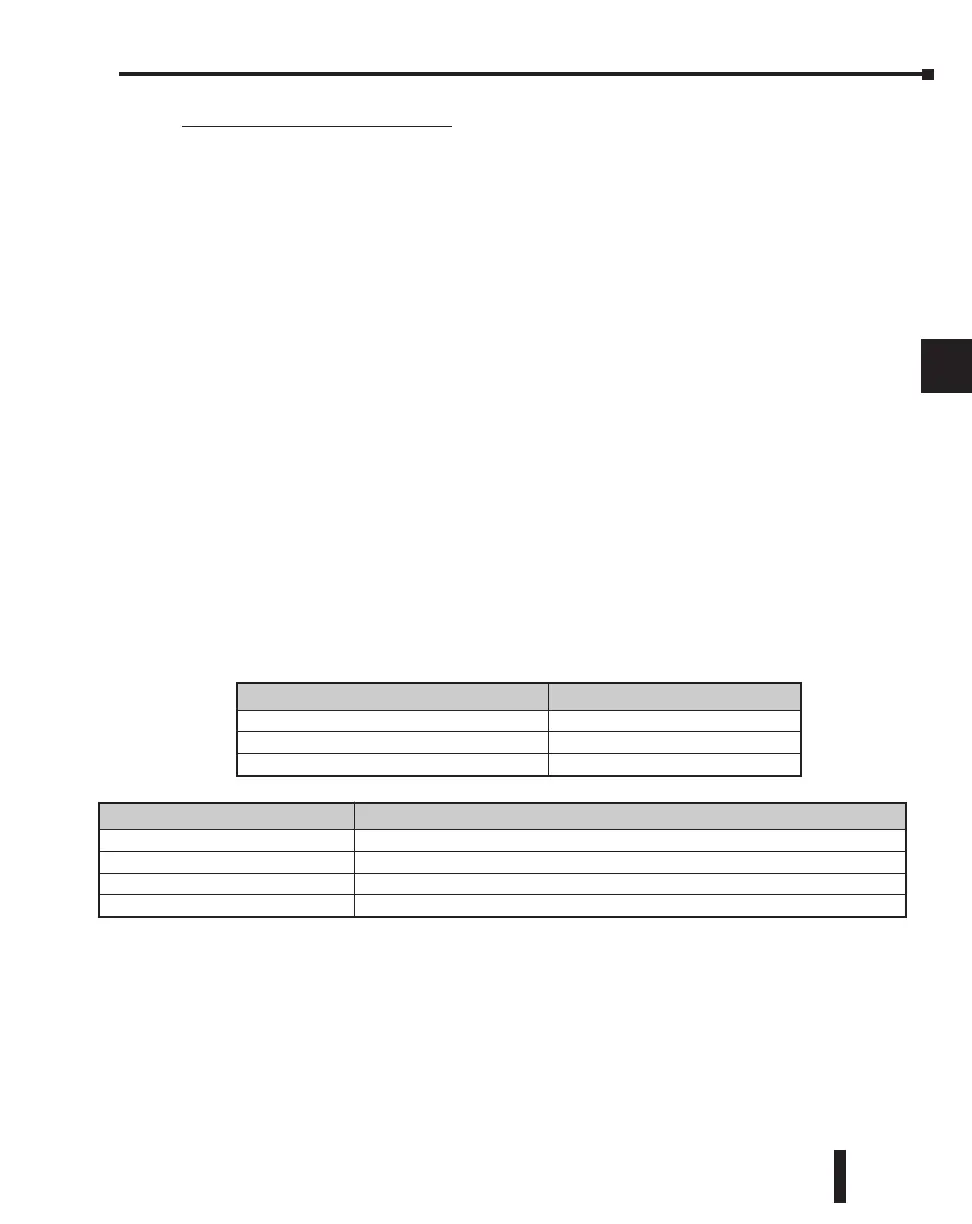

Parameter DL260 Range

Data Destination All V-memory (See page 3 - 56)

Fixed Length K1-128

Bits: Busy, Complete, Timeout Error, Overflow C0-3777

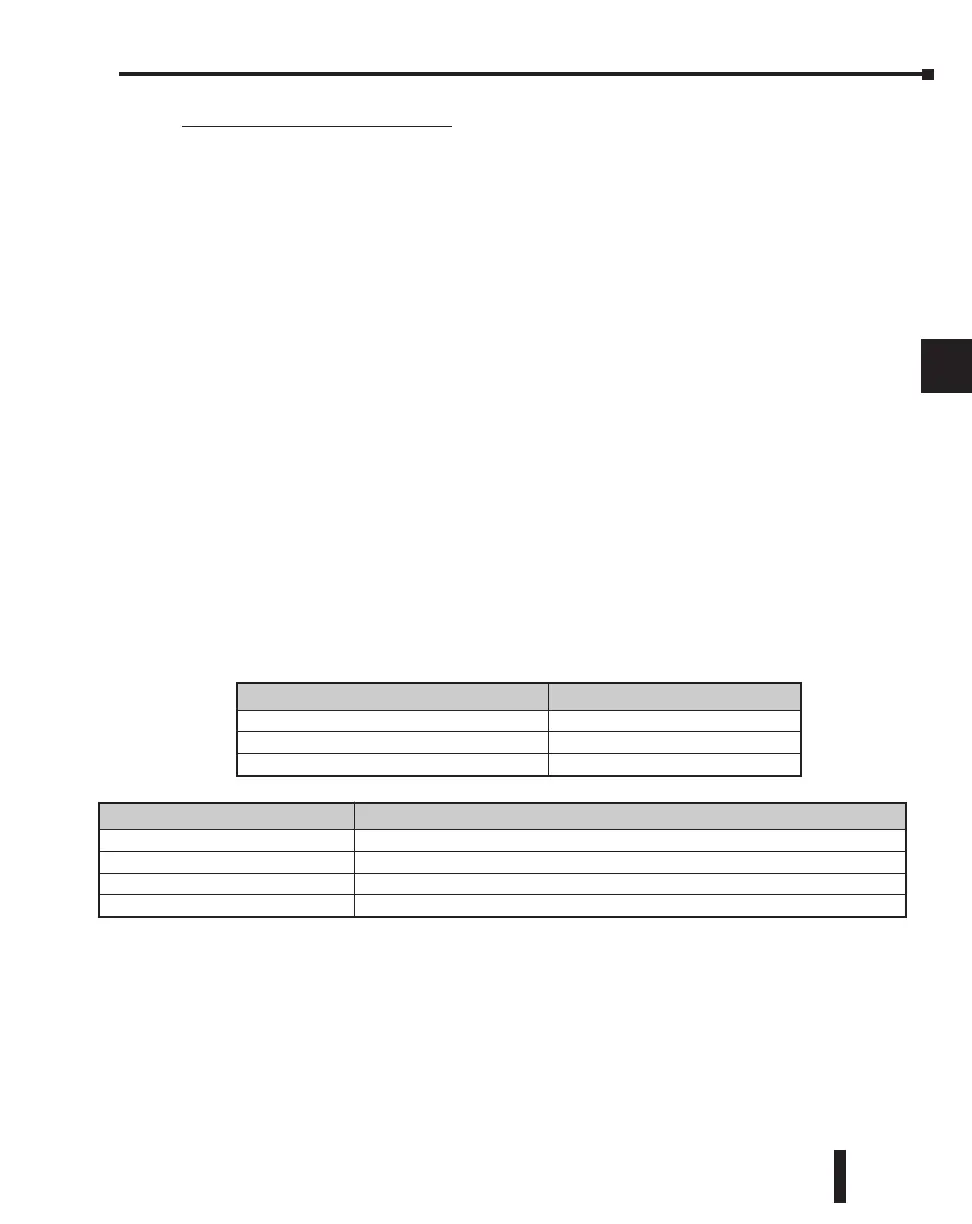

Discrete Bit Flags Description

SP53 On if the CPU cannot execute the instruction.

SP71 On when a value used by the instruction is invalid.

SP116 On when CPU port 2 is communicating with another device.

SP117 On when CPU port 2 has experienced a communication error.

Loading...

Loading...