X1200 Series Router Manual

Page 7-4

Revision 1.3.2

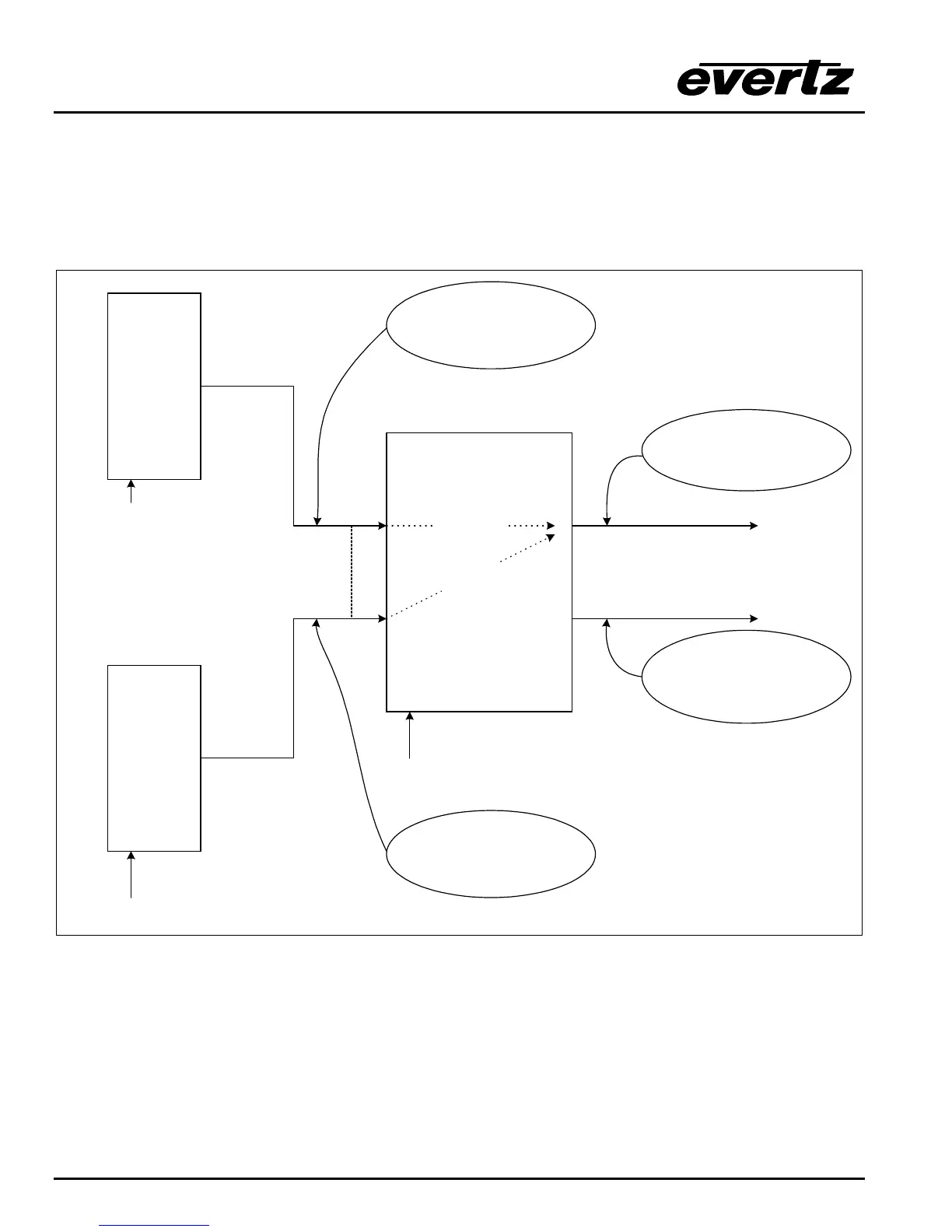

OUTPUT CONFIGURATIONS

7.4. ALL INPUT SIGNALS ARE TIMED WITHIN A RANGE OF +/- 1 LINE

FROM EACH OTHER BUT DELAYED 5 LINES FROM REFERENCE.

This example shows how the router can perform a clean switch on input signals that are delayed by more

than a one from the reference, and are mistimed with respect to each other. The V1 buss output will be

delayed 6 lines with respect to the reference. A clean switch is not attainable on the V2 buss output.

SDI

SOURCE

01

SDI

Source

12

Fine Phase = 0

Course Phase = 6

Clean Switch = on

V1

V2

01

12

REF. Black

REF. Black

REF. Black

X1202 SS Router

1 1/2 Line Delay -

1/2 Line Delay -

SDI Signal 4 1/2 lines.

Delayed W.R.T

Ref. Black

SDI signal Held at

6 Lines Delayed W.R.T.

Ref. Black

Input Dependant

CleanSwitch

"NOT"

attainable

SDI Signal 5 1/2 lines.

Delayed W.R.T

Ref. Black

Figure 7-4: Timing Example 4 – Inputs Not in Time and Delayed from Reference

Loading...

Loading...