CENTRAL PROCESSING UNIT MC68332

5-10 USER’S MANUAL

Table 5-1 Instruction Set Summary

Instruction Syntax Operand Size Operation

ABCD Dn, Dn

– (An), – (An)

8

8

Source

10

+ Destination

10

+ X ⇒ Destination

ADD Dn, <ea>

<ea>, Dn

8, 16, 32

8, 16, 32

Source + Destination ⇒ Destination

ADDA <ea>, An 16, 32 Source + Destination ⇒ Destination

ADDI #<data>, <ea> 8, 16, 32 Immediate data + Destination ⇒ Destination

ADDQ #<data>, <ea> 8, 16, 32 Immediate data + Destination ⇒ Destination

ADDX Dn, Dn

– (An), – (An)

8, 16, 32

8, 16, 32

Source + Destination + X ⇒ Destination

AND <ea>, Dn

Dn, <ea>

8, 16, 32

8, 16, 32

Source · Destination ⇒ Destination

ANDI #<data>, <ea> 8, 16, 32 Data · Destination ⇒ Destination

ANDI to CCR #<data>, CCR 8 Source · CCR ⇒ CCR

ANDI to SR

1

#<data>, SR 16 Source · SR ⇒ SR

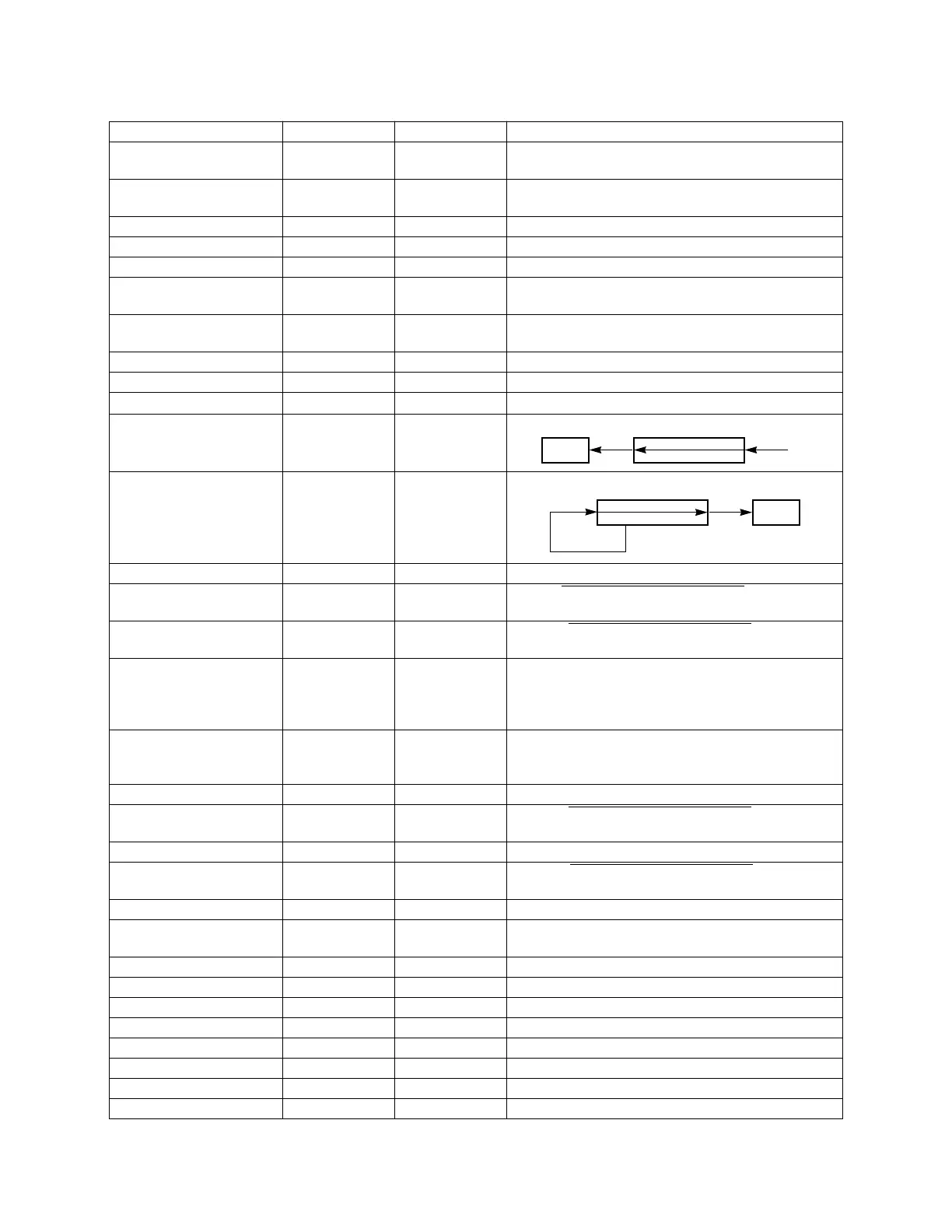

ASL Dn, Dn

#<data>, Dn

Í

8, 16, 32

8, 16, 32

16

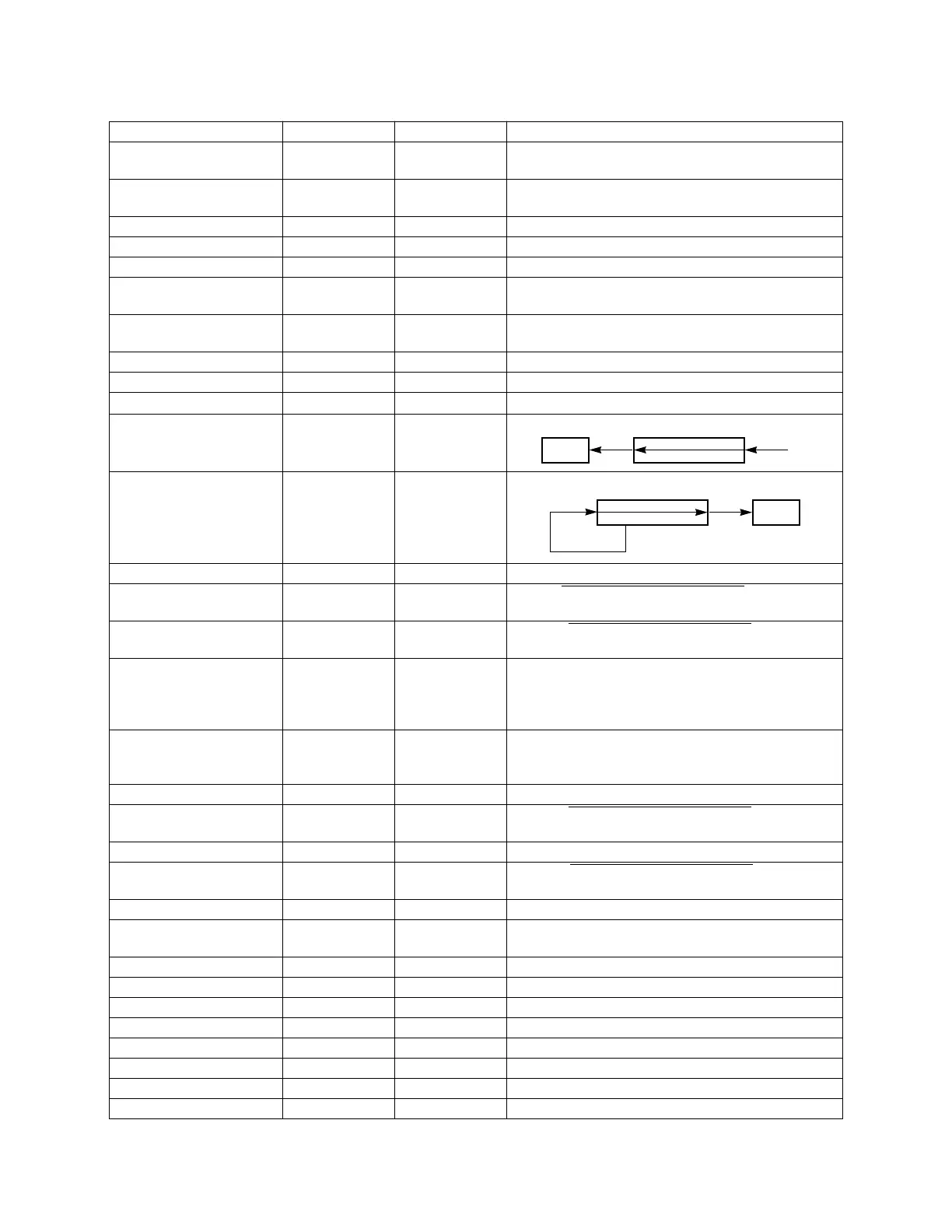

ASR Dn, Dn

#<data>, Dn

Í

8, 16, 32

8, 16, 32

16

Bcc <label> 8, 16, 32 If condition true, then PC + d ⇒ PC

BCHG Dn, <ea>

#<data>, <ea>

8, 32

8, 32

(<bit number> of destination)

⇒ Z ⇒

bit of destination

BCLR Dn, <ea>

#<data>, <ea>

8, 32

8, 32

(<bit number> of destination)

⇒ Z;

0 ⇒ bit of destination

BGND none none If background mode enabled, then enter

background mode, else format/vector offset ⇒

– (SSP);

PC ⇒ – (SSP); SR ⇒ – (SSP); (vector) ⇒ PC

BKPT #<data> none If breakpoint cycle acknowledged, then execute

returned operation word, else trap as illegal

instruction.

BRA <label> 8, 16, 32 PC + d ⇒ PC

BSET Dn, <ea>

#<data>, <ea>

8, 32

8, 32

(<bit number> of destination)

⇒ Z;

1 ⇒ bit of destination

BSR <label> 8, 16, 32 SP – 4 ⇒ SP; PC ⇒ (SP); PC + d ⇒ PC

BTST Dn, <ea>

#<data>, <ea>

8, 32

8, 32

(<bit number> of destination)

⇒ Z

CHK <ea>, Dn 16, 32 If Dn < 0 or Dn < (ea), then CHK exception

CHK2 <ea>, Rn 8, 16, 32 If Rn < lower bound or Rn > upper bound, then

CHK exception

CLR Í 8, 16, 32 0 ⇒ Destination

CMP <ea>, Dn 8, 16, 32 (Destination – Source), CCR shows results

CMPA <ea>, An 16, 32 (Destination – Source), CCR shows results

CMPI #<data>, <ea> 8, 16, 32 (Destination – Data), CCR shows results

CMPA <ea>, An 16, 32 (Destination – Source), CCR shows results

CMPI #<data>, <ea> 8, 16, 32 (Destination – Data), CCR shows results

CMPM (An) +, (An) + 8, 16, 32 (Destination – Source), CCR shows results

<ea>, Rn 8, 16, 32 Lower bound ≤ Rn ≤ Upper bound, CCR shows result

X/C 0

X/C

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...