REGISTER SUMMARY MC68332

D-30 USER’S MANUAL

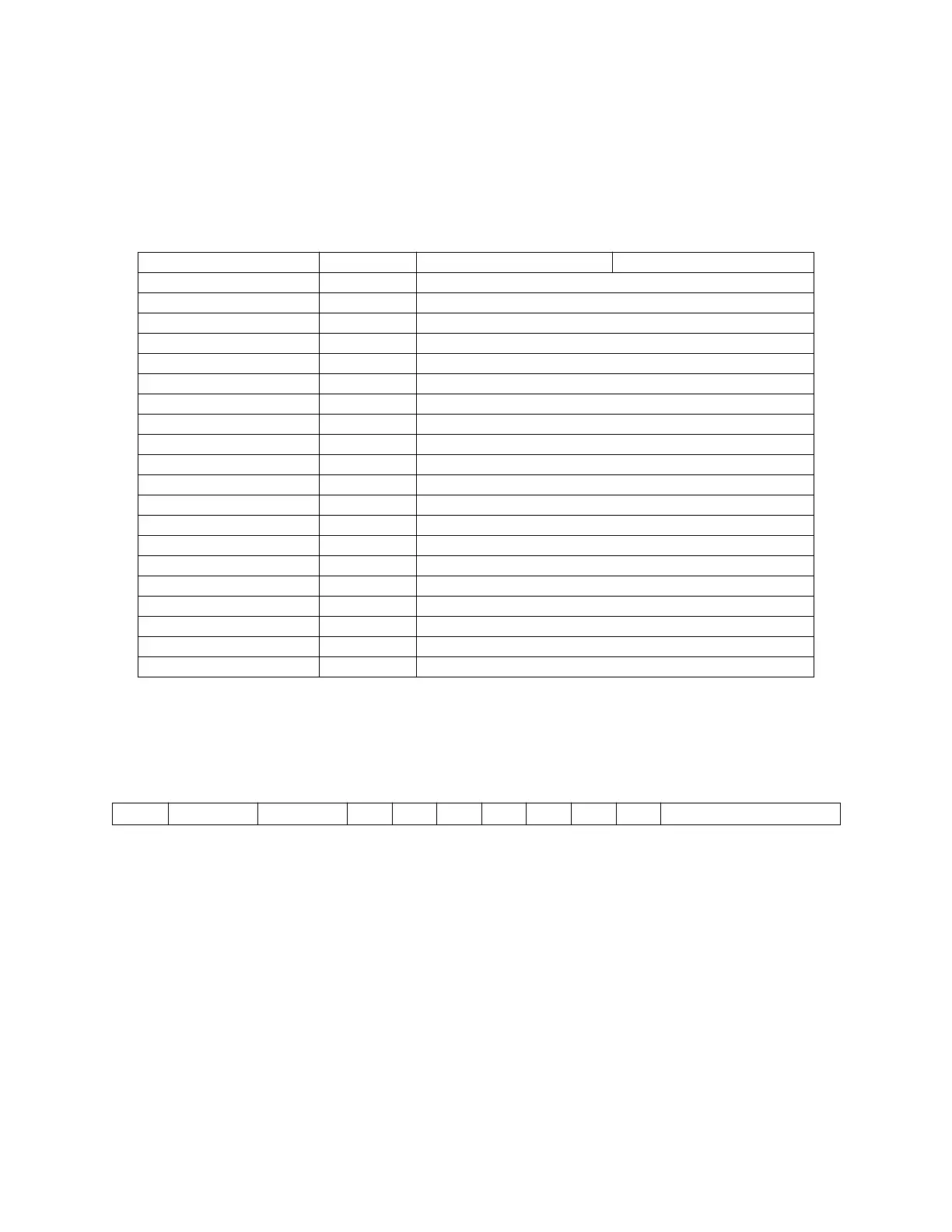

D.5 Time Processor Unit

Table D-5 is the TPU address map. The column labeled “Access” indicates the privi-

lege level at which the CPU must be operating to access the register. A designation of

“S” indicates that supervisor access is required: a designation of “S/U” indicates that

the register can be programmed to the desired privilege level.

Y = M111, where M is the logic state of the module mapping (MM) bit in the SIMCR.

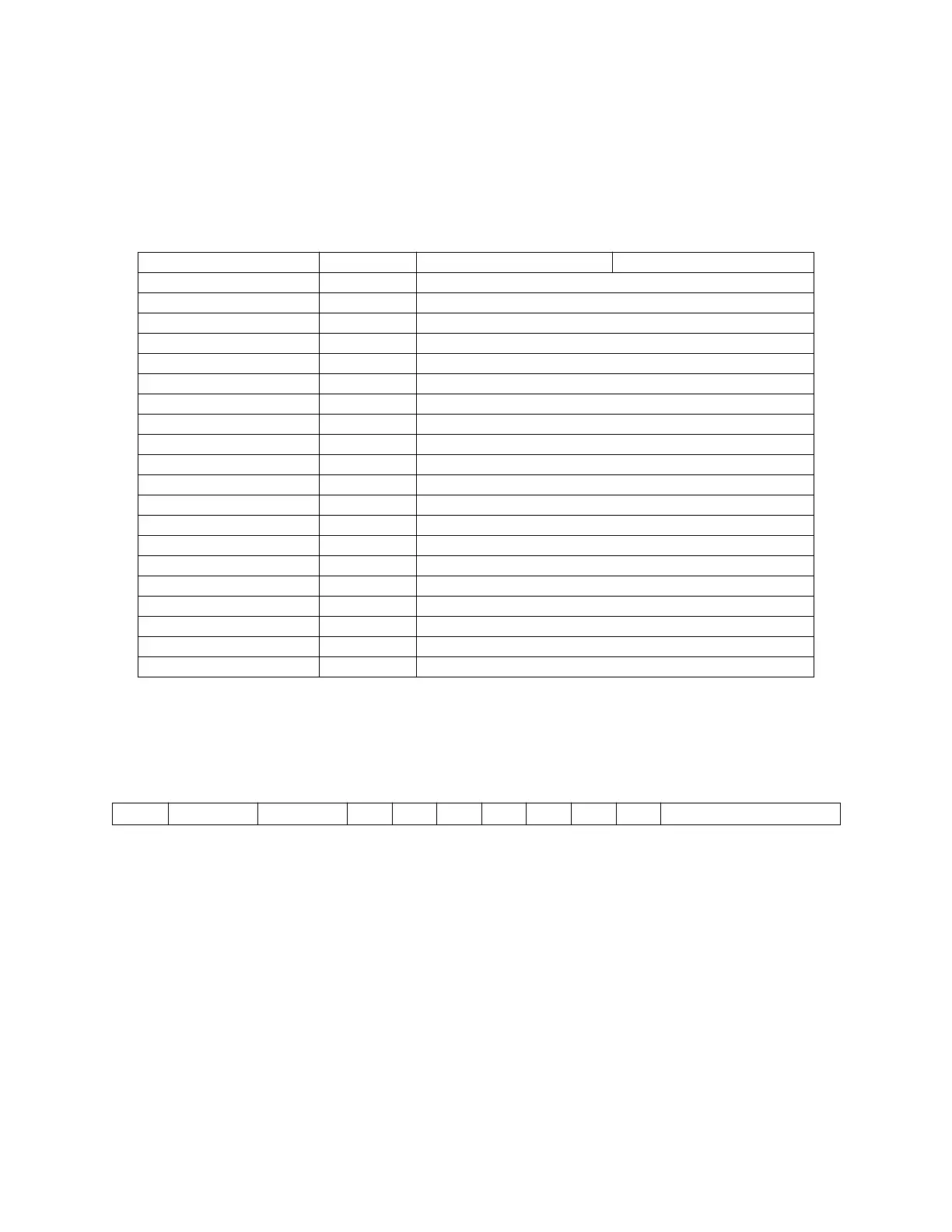

D.5.1 TPUMCR — TPU Module Configuration Register $YFFE00

STOP — Stop Bit

0 = TPU operating normally

1 = Internal clocks shut down

TCR1P — Timer Count Register 1 Prescaler Control

TCR1 is clocked from the output of a prescaler. The prescaler's input is the internal

TPU system clock divided by either 4 or 32, depending on the value of the PSCK bit.

The prescaler divides this input by 1, 2, 4, or 8. Channels using TCR1 have the capa-

bility to resolve down to the TPU system clock divided by 4.

Table D-5 TPU Address Map

Access Address 15 8 7 0

S $YFFE00 TPU MODULE CONFIGURATION REGISTER (TPUMCR)

S $YFFE02 TEST CONFIGURATION REGISTER (TCR)

S $YFFE04 DEVELOPMENT SUPPORT CONTROL REGISTER (DSCR)

S $YFFE06 DEVELOPMENT SUPPORT STATUS REGISTER (DSSR)

S $YFFE08 TPU INTERRUPT CONFIGURATION REGISTER (TICR)

S $YFFE0A CHANNEL INTERRUPT ENABLE REGISTER (CIER)

S $YFFE0C CHANNEL FUNCTION SELECTION REGISTER 0 (CFSR0)

S $YFFE0E CHANNEL FUNCTION SELECTION REGISTER 1 (CFSR1)

S $YFFE10 CHANNEL FUNCTION SELECTION REGISTER 2 (CFSR2)

S $YFFE12 CHANNEL FUNCTION SELECTION REGISTER 3 (CFSR3)

S/U $YFFE14 HOST SEQUENCE REGISTER 0 (HSQR0)

S/U $YFFE16 HOST SEQUENCE REGISTER 1 (HSQR1)

S/U $YFFE18 HOST SERVICE REQUEST REGISTER 0 (HSRR0)

S/U $YFFE1A HOST SERVICE REQUEST REGISTER 1 (HSRR1)

S $YFFE1C CHANNEL PRIORITY REGISTER 0 (CPR0)

S $YFFE1E CHANNEL PRIORITY REGISTER 1 (CPR1)

S $YFFE20 CHANNEL INTERRUPT STATUS REGISTER (CISR)

S $YFFE22 LINK REGISTER (LR)

S $YFFE24 SERVICE GRANT LATCH REGISTER (SGLR)

S $YFFE26 DECODED CHANNEL NUMBER REGISTER (DCNR)

15 14 13 12 11 10 9 8 7 6 5 4 3 0

STOP TCR1P TCR2P EMU T2CG STF SUPV PSCK 0 0 IARB

RESET:

0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...