REGISTER SUMMARY MC68332

D-32 USER’S MANUAL

PSCK — Prescaler Clock

0 = System clock/32 is input to TCR1 prescaler

1 = System clock/4 is input to TCR1 prescaler

IARB — Interrupt Arbitration

Each module that generates interrupts must have an IARB value. IARB values are

used to arbitrate between interrupt requests of the same priority.

D.5.2 TCR — Test Configuration Register $YFFE02

The TCR is used for factory test of the MCU.

D.5.3 DSCR — Development Support Control Register $YFFE04

HOT4 — Hang on T4

0 = Exit wait on T4 state caused by assertion of HOT4

1 = Enter wait on T4 state

BLC — Branch Latch Control

0 = Latch conditions into branch condition register before exiting halted state.

1 = Do not latch conditions into branch condition register before exiting the halted

state or during the time-slot transition period.

CLKS — Stop Clocks (to TCRs)

0 = Do not stop TCRs.

1 = Stop TCRs during the halted state.

FRZ[1:0] — IMB FREEZE Response

The FRZ bits specify the TPU microengine response to the FREEZE signal.

CCL — Channel Conditions Latch

CCL controls the latching of channel conditions (MRL and TDL) when the CHAN reg-

ister is written.

0 = Only the pin state condition of the new channel is latched as a result of the write

CHAN register microinstruction.

1 = Pin state, MRL, and TDL conditions of the new channel are latched as a result

of a write CHAN register microinstruction.

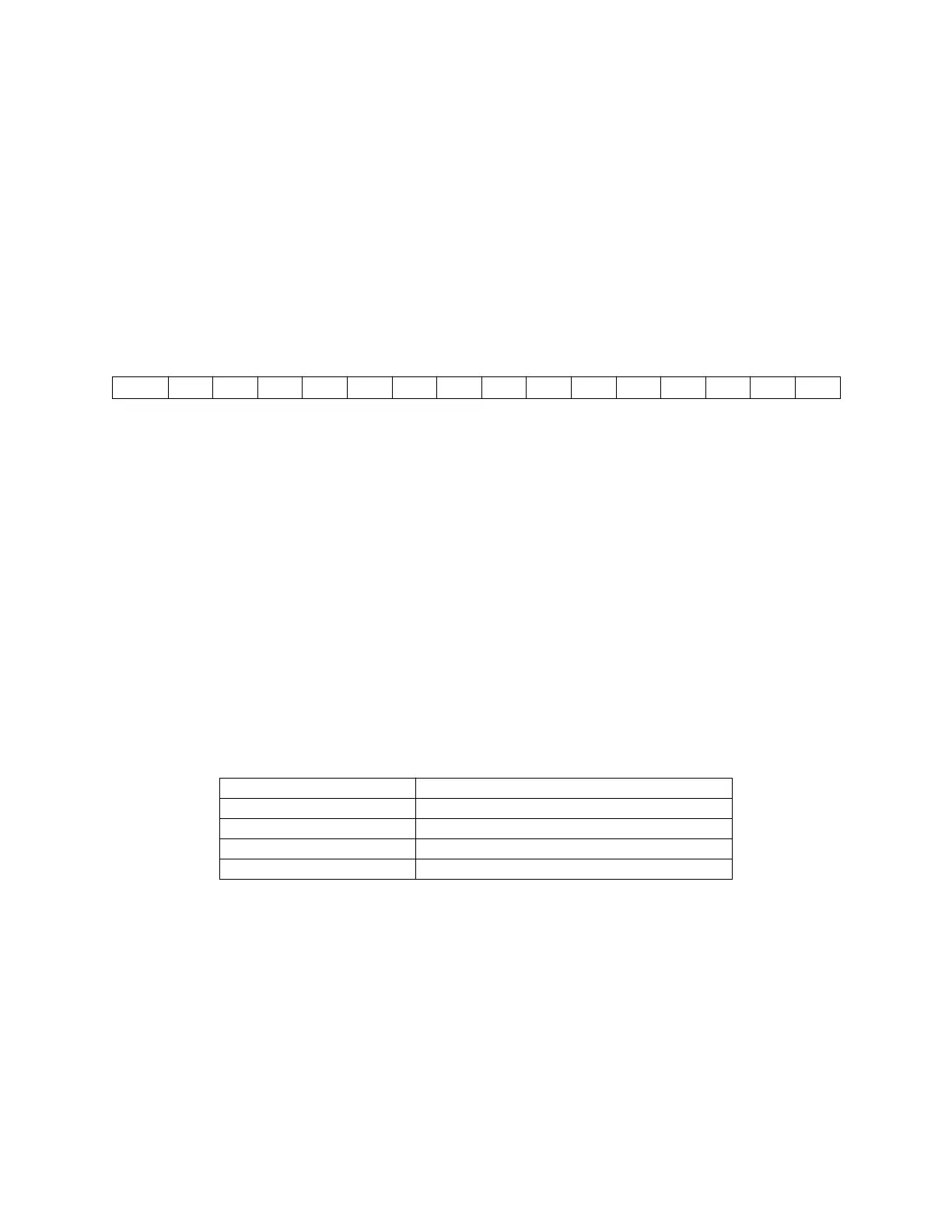

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

HOT4 0 0 0 0 BLC CLKS FRZ1 FRZ0 CCL BP BC BH BL BM BT

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

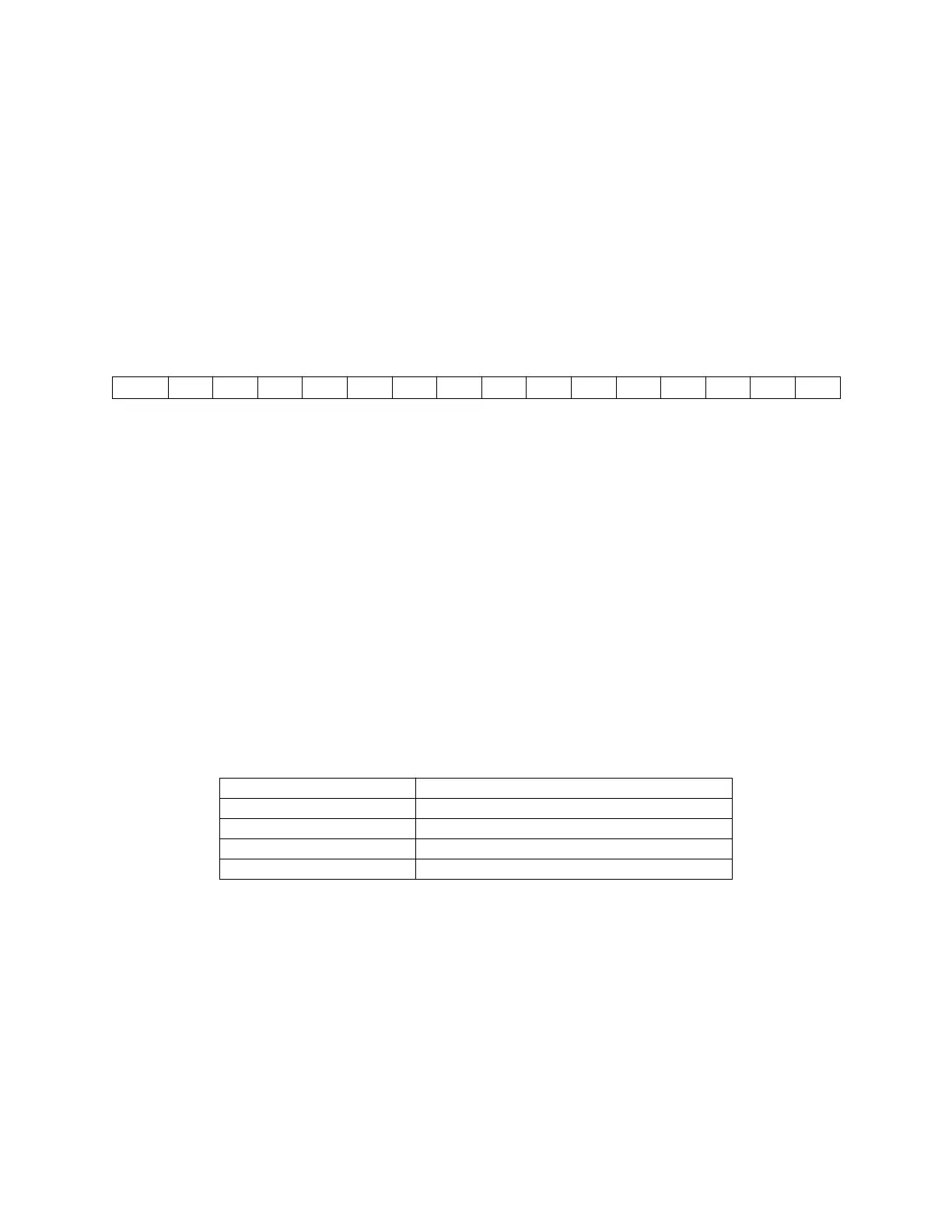

FRZ[1:0] TPU Response

00 Ignore Freeze

01 Reserved

10 Freeze at End of Current Microcycle

11 Freeze at Next Time-Slot Boundary

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...