MC68332 REGISTER SUMMARY

USER’S MANUAL D-33

BP, BC, BH, BL, BM, and BT — Breakpoint Enable Bits

DSCR[5:0] are TPU breakpoint enables. Setting a bit enables a breakpoint condition.

BP — Break if mPC equals mPC breakpoint register.

BC — Break if CHAN register equals channel breakpoint register at beginning of state

or when CHAN is changed through microcode.

BH — Break if host service latch is asserted at beginning of state.

BL — Break if link service latch is asserted at beginning of state.

BM — Break if MRL is asserted at beginning of state.

BT — Break if TDL is asserted at beginning of state.

D.5.4 DSSR — Development Support Status Register $YFFE06

BKPT — Breakpoint Asserted Flag

If an internal breakpoint caused the TPU to enter the halted state, the TPU asserts the

BKPT signal on the IMB and the BKPT flag. The TPU continues to assert BKPT until

it recognizes a breakpoint acknowledge cycle from a host, or until the FREEZE signal

on the IMB is asserted.

PCBK — µPC Breakpoint Flag

PCBK is asserted if a breakpoint occurs because of a µPC register match with the µPC

breakpoint register. PCBK is negated when the BKPT flag is negated.

CHBK — Channel Register Breakpoint Flag

CHBK is asserted if a breakpoint occurs because of a CHAN register match with the

channel register breakpoint register. CHBK is negated when the BKPT flag is negated.

SRBK — Service Request Breakpoint Flag

SRBK is asserted if a breakpoint occurs because of any of the service request latches

being asserted along with their corresponding enable flag in the development support

control register. SRBK is negated when the BKPT flag is negated.

TPUF — TPU FREEZE Flag

TPUF is asserted whenever the TPU is in a halted state as a result of FREEZE being

asserted. This flag is automatically negated when the TPU exits the halted state be-

cause of FREEZE being negated.

D.5.5 TICR — TPU Interrupt Configuration Register $YFFE08

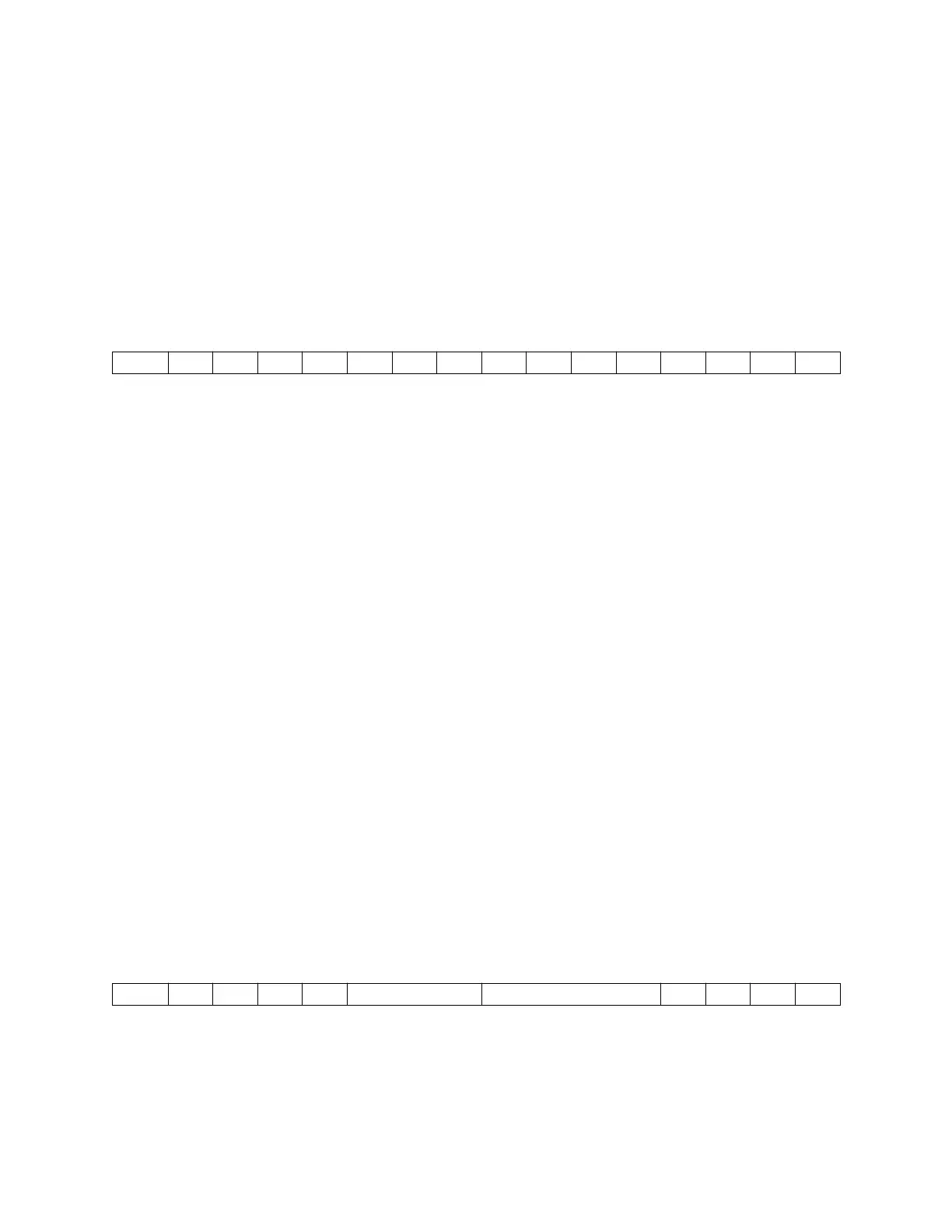

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 0 BKPT PCBK CHBK SRBK TPUF 0 0 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

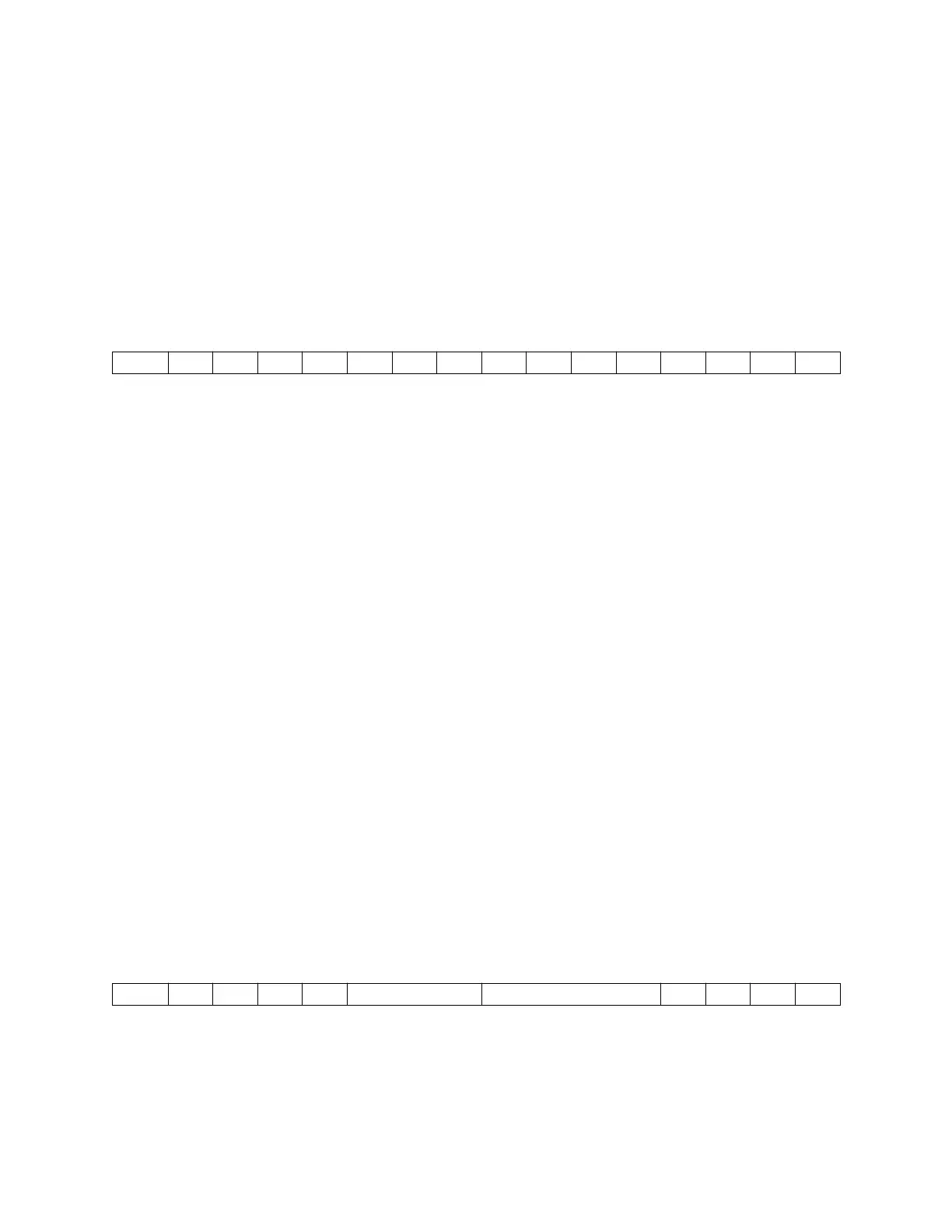

15 14 13 12 11 10 8 7 4 3 2 1 0

0 0 0 0 0 CIRL CIBV 0 0 0 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...