REGISTER SUMMARY MC68332

D-36 USER’S MANUAL

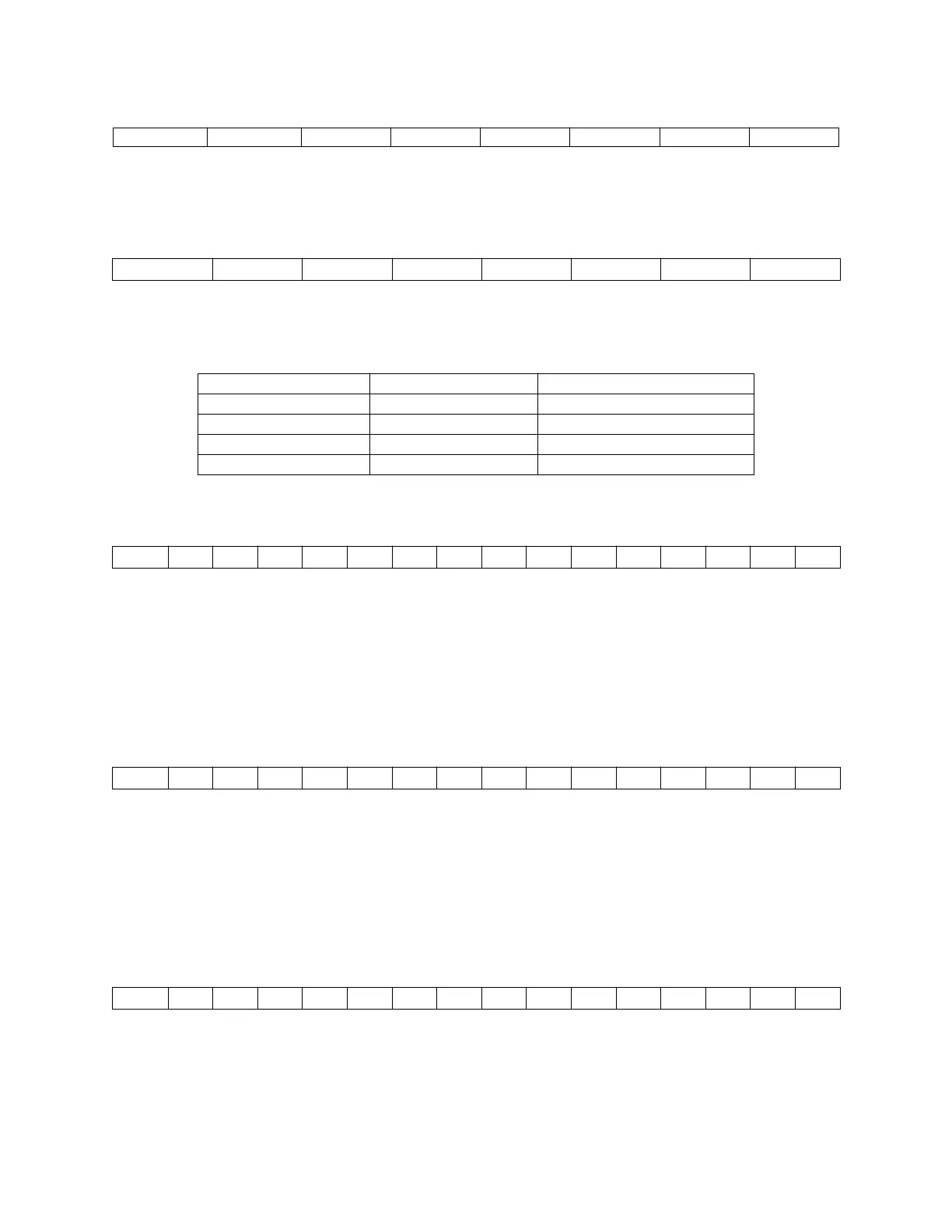

D.5.15 CPR0 — Channel Priority Register 0 $YFFE1C

D.5.16 CPR1 — Channel Priority Register 1 $YFFE1E

CH[15:0] — Encoded One of Three Channel Priority Levels

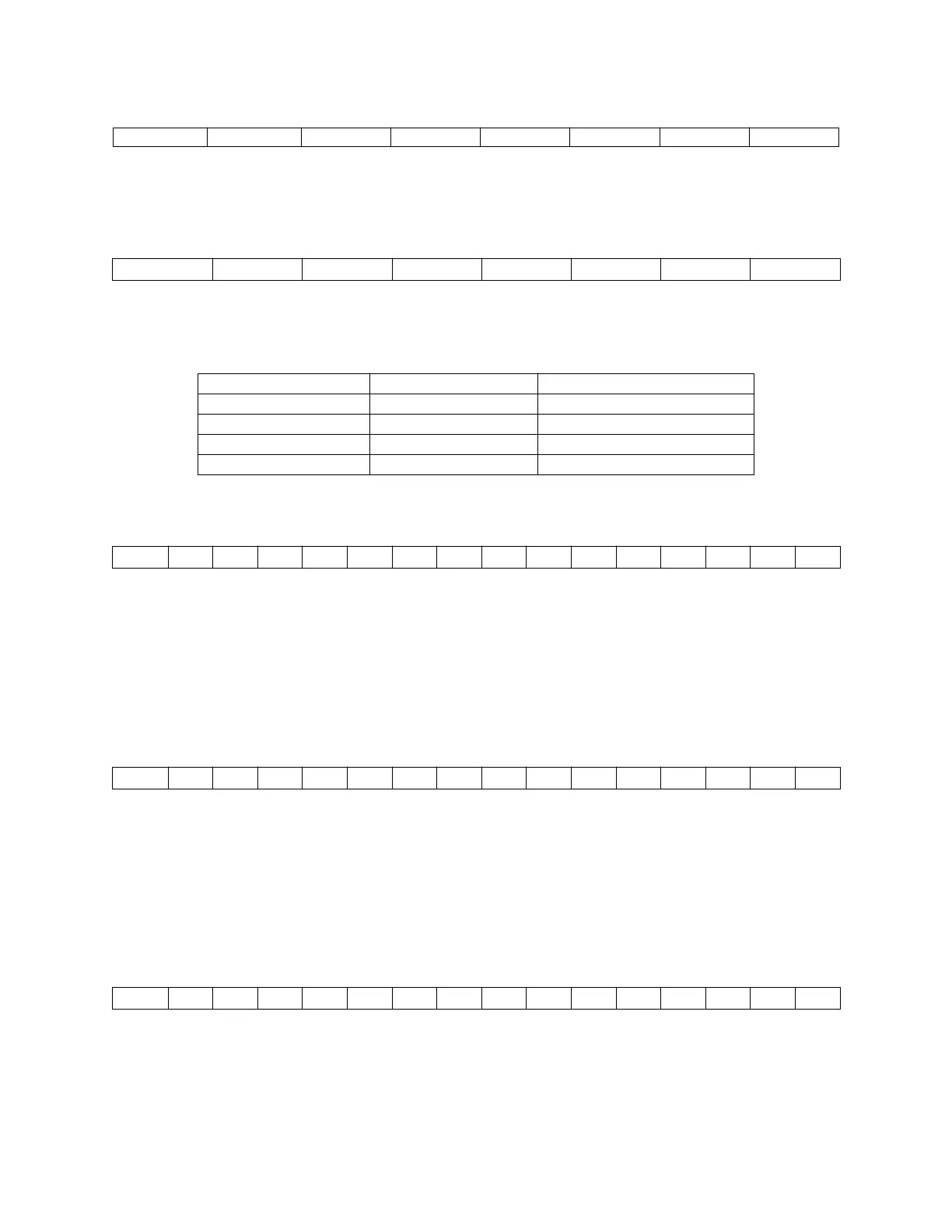

D.5.17 CISR — Channel Interrupt Status Register $YFFE20

CH[15:0] — Channel Interrupt Status Bit

0 = Channel interrupt not asserted

1 = Channel interrupt asserted

D.5.18 LR — Link Register $YFFE22

CH[15:0] — Test Mode Link Service Request Enable Bit

0 = Link bit not asserted

1 = Link bit asserted

D.5.19 SGLR — Service Grant Latch Register $YFFE24

CH[15:0] — Service Granted Bits

1514131211109876543210

CH 15 CH 14 CH13 CH 12 CH 11 CH 10 CH 9 CH 8

RESET:

0 00 0000000000000

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CH 7 CH 6 CH 5 CH 4 CH 3 CH 2 CH 1 CH 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

CHX[1:0] Service Guaranteed Time Slots

00 Disabled —

01 Low 1 out of 7

10 Middle 2 out of 7

11 High 4 out of 7

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CH 15 CH 14 CH 13 CH 12 CH 11 CH 10 CH 9 CH 8 CH 7 CH 6 CH 5 CH 4 CH 3 CH 2 CH 1 CH 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CH 15 CH 14 CH 13 CH 12 CH 11 CH 10 CH 9 CH 8 CH 7 CH 6 CH 5 CH 4 CH 3 CH 2 CH 1 CH 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CH 15 CH 14 CH 13 CH 12 CH 11 CH 10 CH 9 CH 8 CH 7 CH 6 CH 5 CH 4 CH 3 CH 2 CH 1 CH 0

RESET:

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...