SYSTEM INTEGRATION MODULE MC68332

4-6 USER’S MANUAL

Perform a software watchdog service sequence as follows:

1. Write $55 to SWSR.

2. Write $AA to SWSR.

Both writes must occur before time-out in the order listed, but any number of instruc-

tions can be executed between the two writes.

Watchdog clock rate is affected by the software watchdog prescale (SWP) and soft-

ware watchdog timing (SWT) fields in SYPCR.

SWP determines system clock prescaling for the watchdog timer and determines that

one of two options, either no prescaling or prescaling by a factor of 512, can be select-

ed. The value of SWP is affected by the state of the MODCLK pin during reset, as

shown in Table 4-3. System software can change SWP value.

The SWT field selects the divide ratio used to establish software watchdog time-out

period. Time-out period is given by the following equations.

or

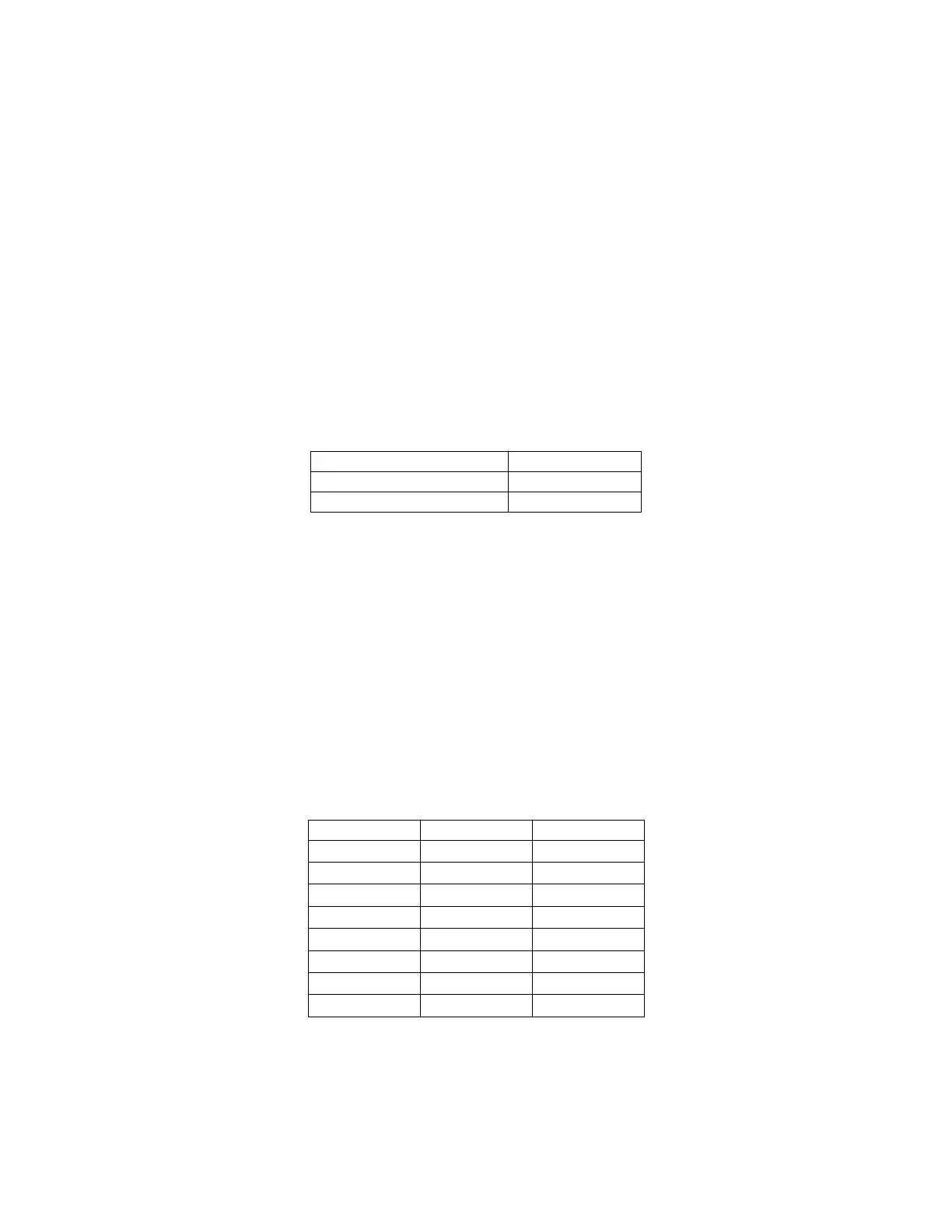

Table 4-4 shows the ratio for each combination of SWP and SWT bits. When SWT[1:0]

are modified, a watchdog service sequence must be performed before the new time-

out period can take effect.

Figure 4-3 is a block diagram of the watchdog timer and the clock control for the pe-

riodic interrupt timer.

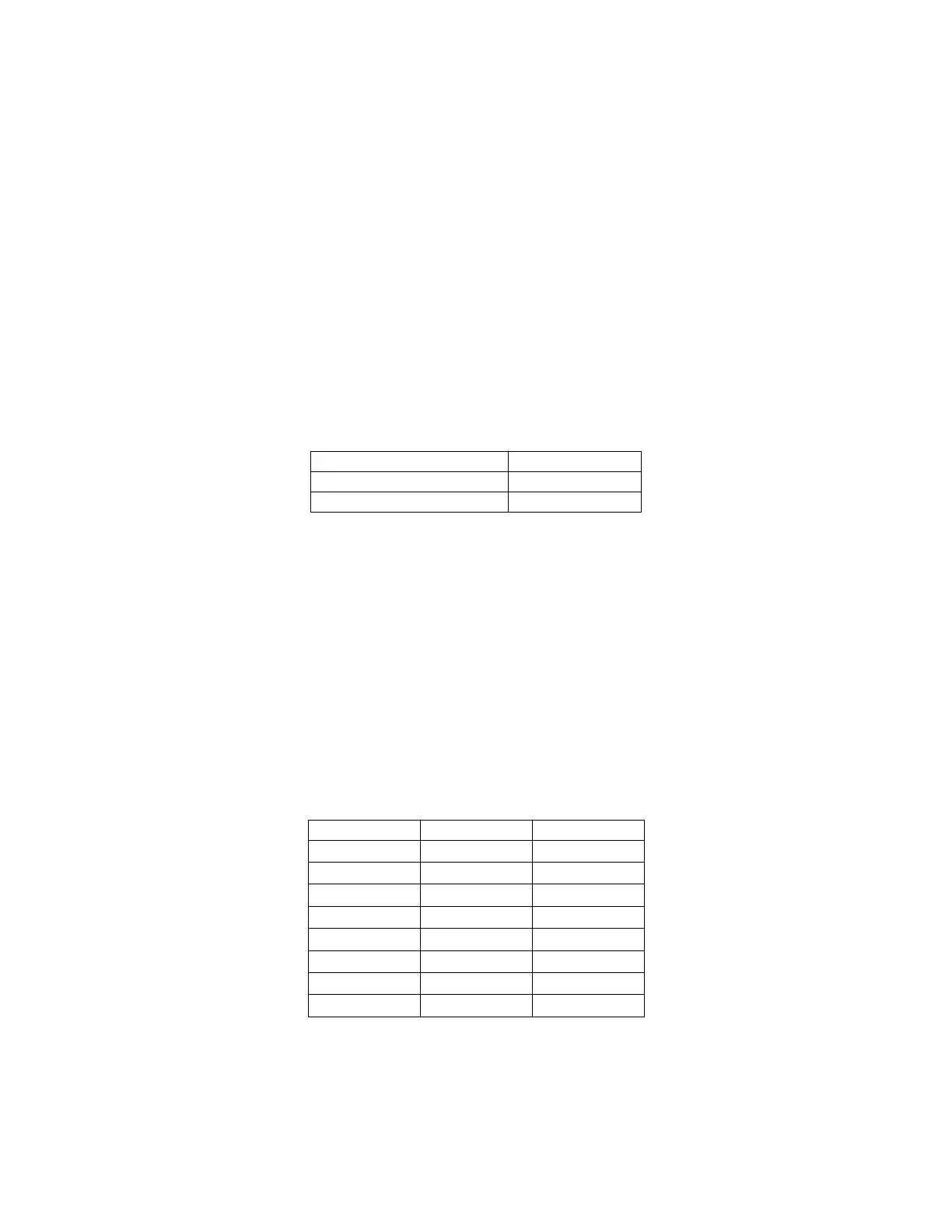

Table 4-3 MODCLK Pin and

SWP Bit During Reset

MODCLK SWP

0 (External Clock) 1 (÷ 512)

1 (Internal Clock) 0 (÷ 1)

Table 4-4 Software Watchdog Ratio

SWP SWT Ratio

000

2

9

001

2

11

010

2

13

011

2

15

100

2

18

101

2

20

110

2

22

111

2

24

Time-out Period

1

EXTAL Frequency Divide Ratio⁄

-------------------------------------------------------------------------------------=

Time-out Period

Divide Ratio

EXTAL Frequency

-------------------------------------------------=

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...