SYSTEM INTEGRATION MODULE MC68332

4-32 USER’S MANUAL

Retry Termination

HALT

and BERR are asserted in lieu of, at the same time as, or before DSACK or

after DSACK

; BERR is negated at the same time or after DSACK; HALT may be

negated at the same time or after BERR

.

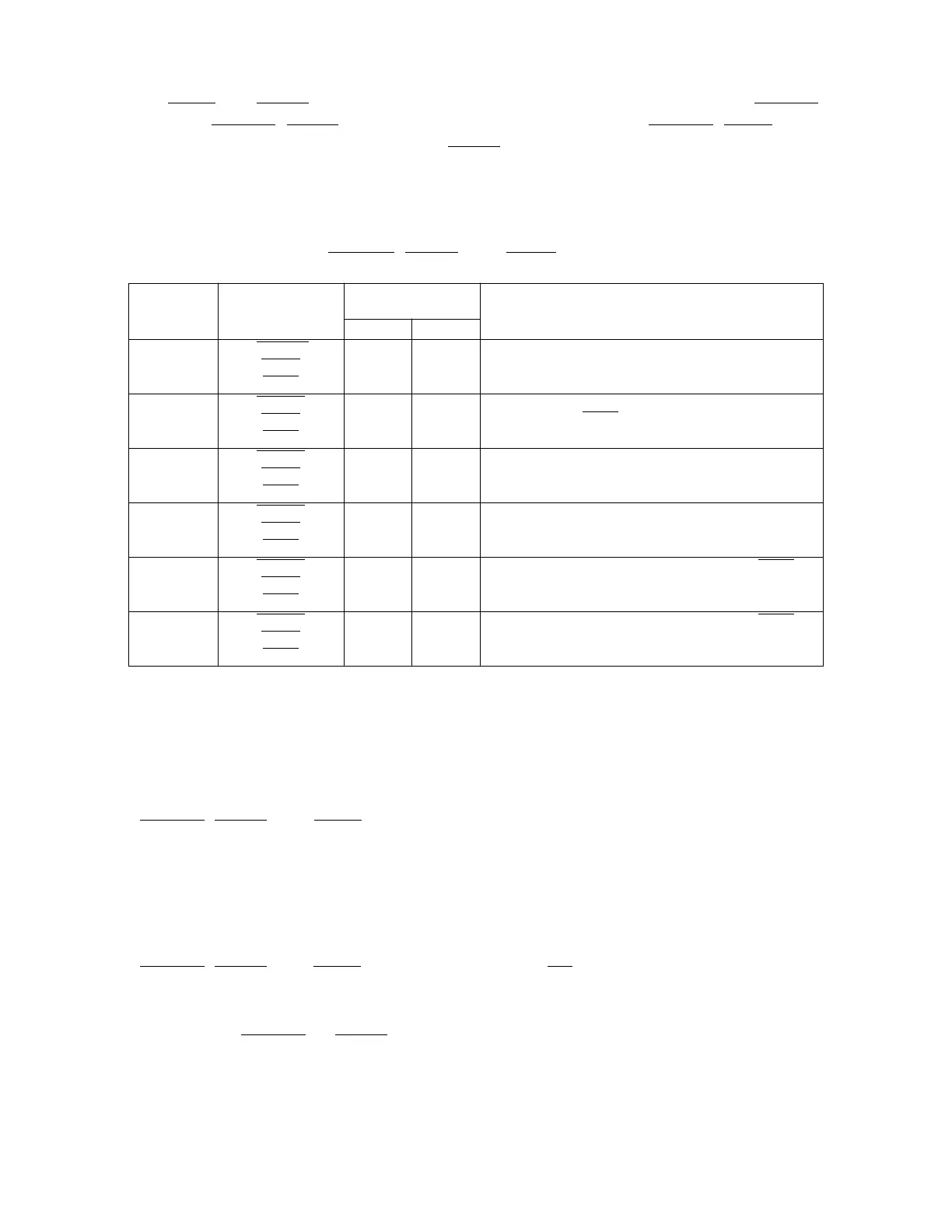

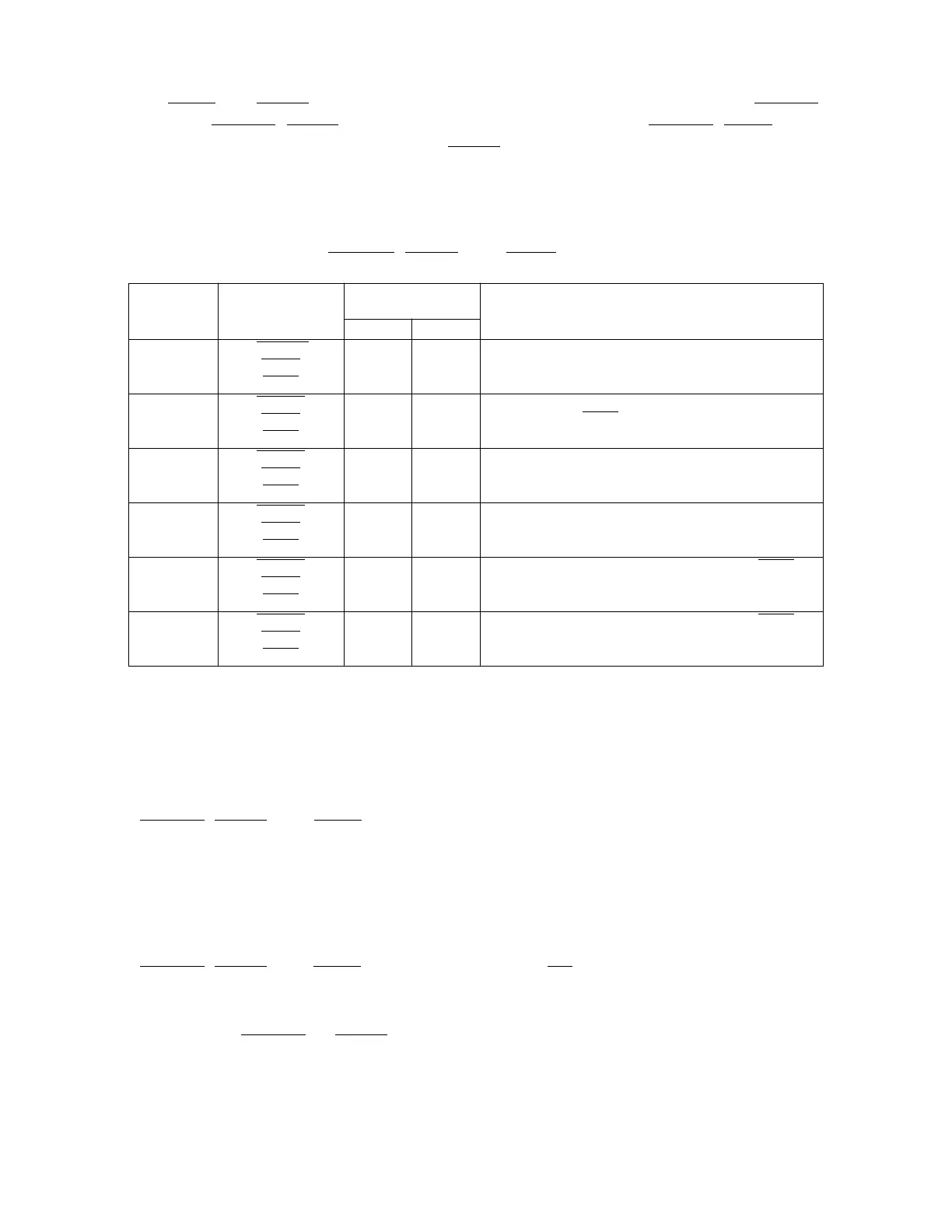

Table 4-14 shows various combinations of control signal sequences and the resulting

bus cycle terminations.

NOTES:

N = The number of current even bus state (S2, S4, etc.).

A = Signal is asserted in this bus state.

NA = Signal is not asserted in this state

X = Don't care.

S = Signal was asserted in previous state and remains asserted in this state.

To properly control termination of a bus cycle for a retry or a bus error condition,

DSACK

, BERR, and HALT must be asserted and negated with the rising edge of the

MCU clock. This ensures that when two signals are asserted simultaneously, the re-

quired setup time and hold time for both of them are met for the same falling edge of

the MCU clock. (Refer to APPENDIX A ELECTRICAL CHARACTERISTICS for timing

requirements.) External circuitry that provides these signals must be designed with

these constraints in mind, or else the internal bus monitor must be used.

DSACK

, BERR, and HALT may be negated after AS is negated.

WARNING

If DSACK

or BERR remain asserted into S2 of the next bus cycle,

that cycle may be terminated prematurely.

Table 4-14 DSACK

, BERR, and HALT Assertion Results

Case

Number

Control Signal Asserted on Rising

Edge of State

Result

N N + 2

1 DSACK

BERR

HALT

A

NA

NA

S

NA

X

Normal termination.

2 DSACK

BERR

HALT

A

NA

A/S

S

NA

S

Halt termination: normal cycle terminate and halt.

Continue when HALT

is negated.

3 DSACK

BERR

HALT

NA/A

A

NA

X

S

X

Bus error termination: terminate and take bus error

exception, possibly deferred.

4 DSACK

BERR

HALT

A

A

NA

X

S

NA

Bus error termination: terminate and take bus error

exception, possibly deferred.

5 DSACK

BERR

HALT

NA/A

A

A/S

X

S

S

Retry termination: terminate and retry when HALT is

negated.

6 DSACK

BERR

HALT

A

NA

NA

X

A

A

Retry termination: terminate and retry when HALT is

negated.

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...