rewrites) the primary CPB completely. Once the primary CPB is valid, it is safe to modify the secondary CPB. When rewriting,

the magic number at the start of a CPB is the last word written in the CPB. (After this number is written only image pointer

slot values can be changed.)

When the client writes the application image to flash, it ensures that the pointers within the main image pointer of its first

signature block are updated to point to the correct locations in flash. When using HPS to manage RSU, both the U-Boot and

LIBRSU clients implement the required pointer updates. For more information, refer to the Application Image Layout section.

Note: In order to successfully perform CPB compression, the HPS software (U-Boot or Linux) must be configured to have a QSPI

erase granularity of 32 KB or less. When configured with a coarser erase granularity (like 64 KB for example), the operation

fails. All supported flash devices offer erase granularities of 4 KB, 32 KB, and 64 KB, and the default for the current HPS

software is 4 KB.

5.4.2.5. Application Image Layout

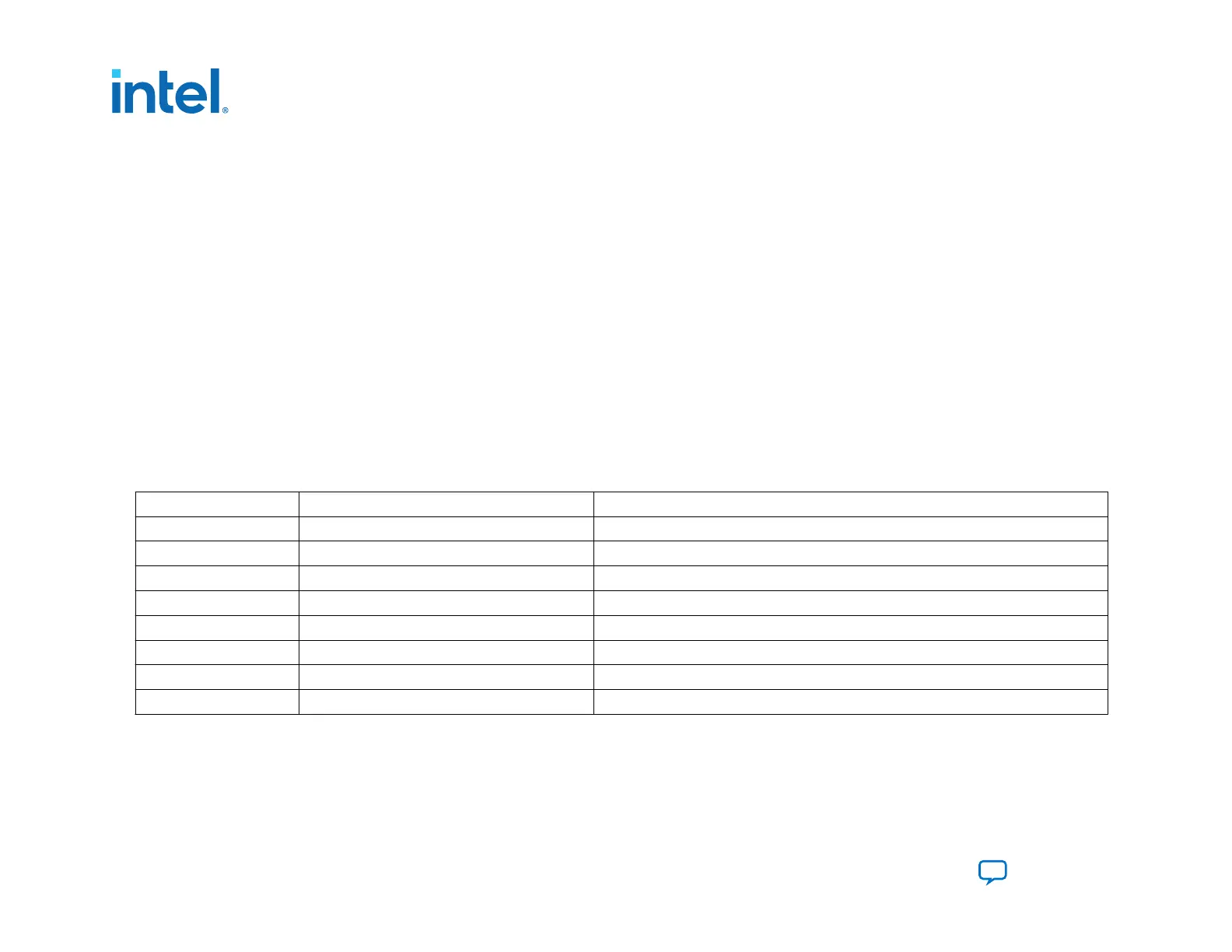

The application image comprises SDM firmware and the configuration data. The configuration data includes up to four

sections. The SDM firmware contains pointers to those sections. The table below shows the location of the number of sections

and the section pointers in a application image.

Table 51. Application Image Section Pointers

Offset Size (in bytes) Description

0x1F00 4 Number of sections

…

0x1F08 8 Address of 1st section

0x1F10 8 Address of 2nd section

0x1F18 8 Address of 3rd section

0x1F20 8 Address of 4th section

…

0x1FFC 4 CRC32 of 0x1000 to 0x1FFB

5. Remote System Update (RSU)

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

180

Loading...

Loading...