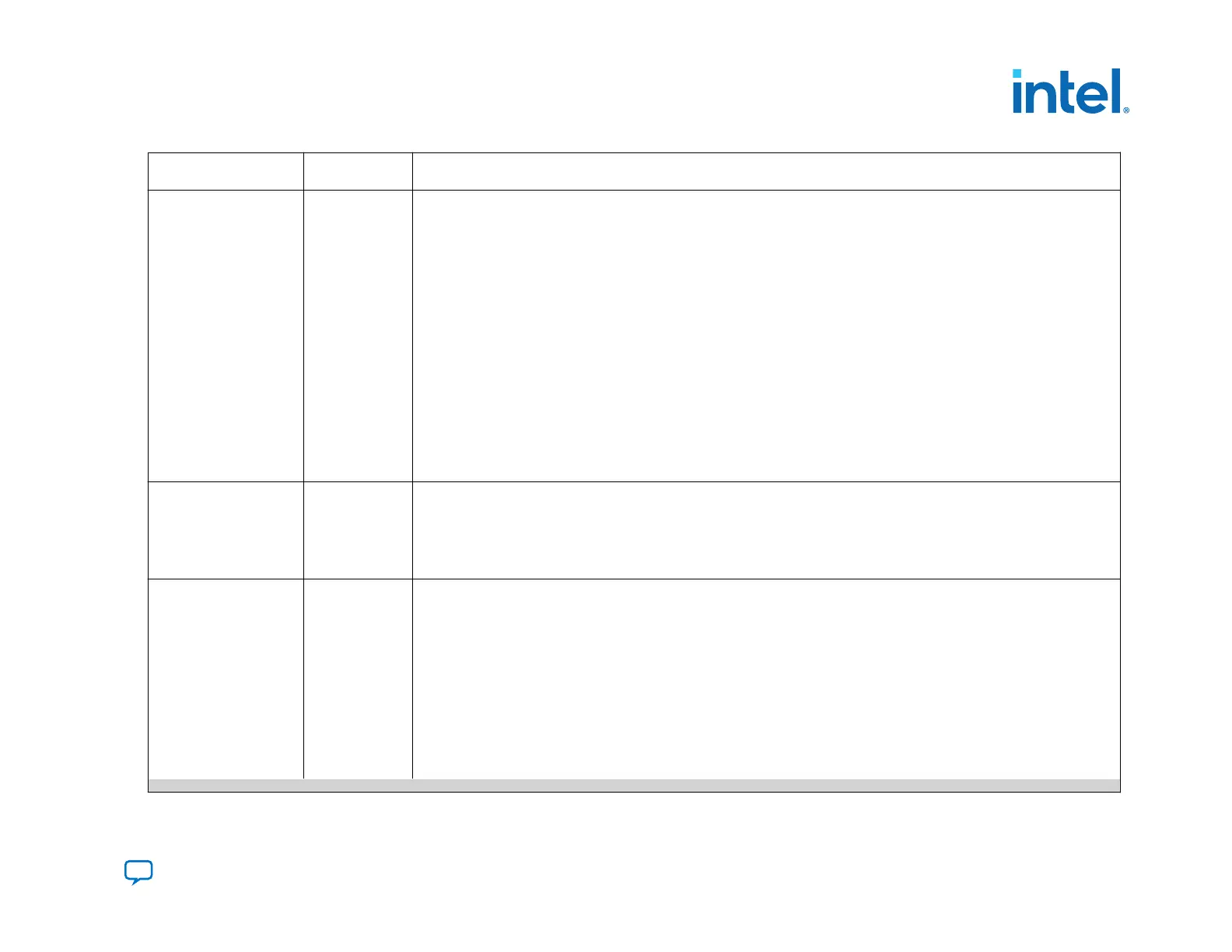

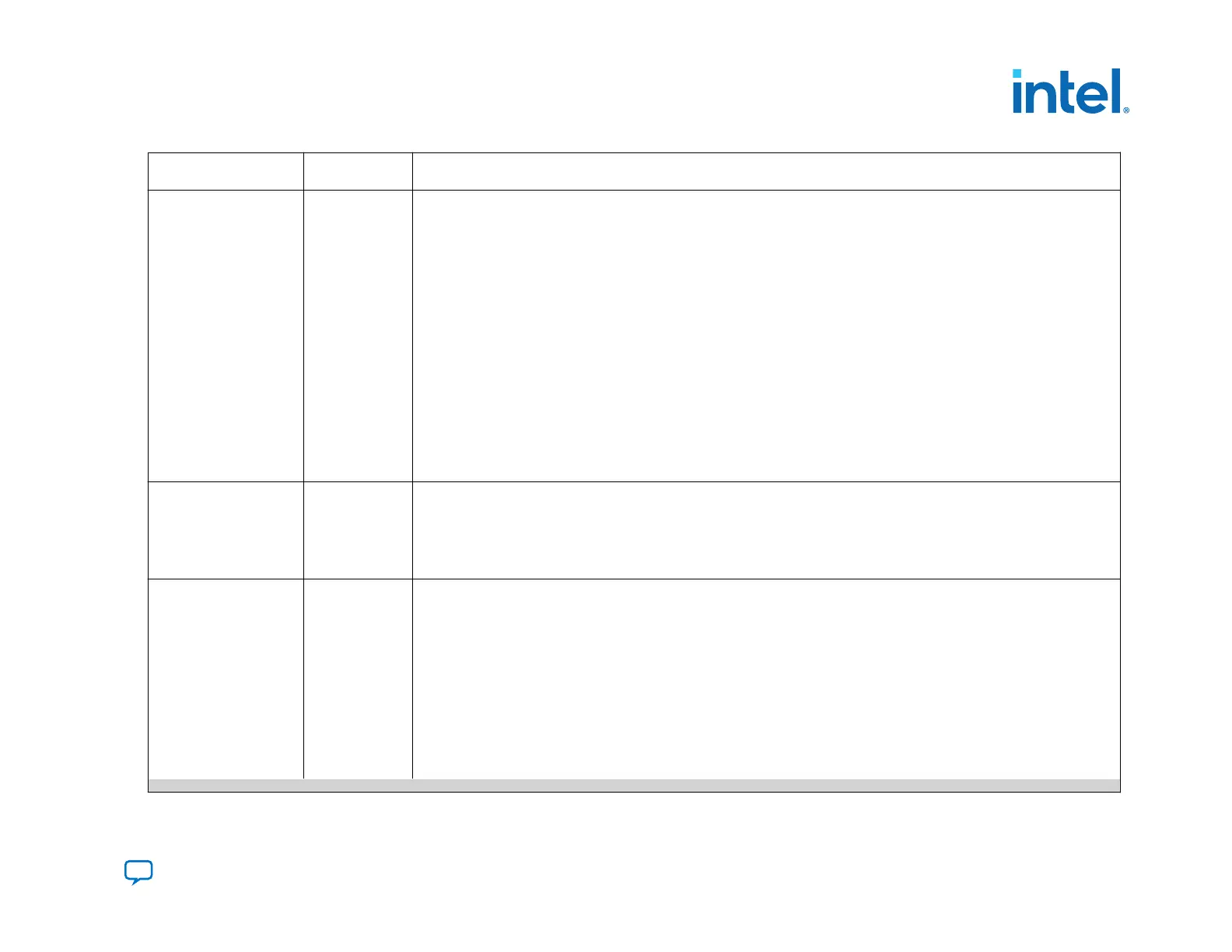

Document Version Intel Quartus

Prime Version

Changes

• Moved nCONFIG, nSTATUS, CONF_DONE and INIT_DONE, and SDM_IO Pins sections from Understanding and

Troubleshooting Configuration Pin Behavior to Specifying Optional Configuration Pins.

— Removed debugging suggestions sections.

— Revised resistor value from 25 kΩ to 20kΩ in the SDM_IO Pins section.

•

Updated nSTATUS topic to clarify nSTATUS during the V

CCIO_SDM

ramp up.

• Updated the Command List and Description table:

—

Corrected response length from 1 to 0 for the QSPI_OPEN, QSPI_CLOSE and QSPI_SET_CS command.

—

Revised RSU_IMAGE_UPDATE command description to include information about resetting QSPI flash and behavior

between the external host and FPGA.

—

Revised QSPI_OPEN, QSPI_WRITE, QSPI_READ_DEVICE_REG, and QSPI_WRITE_DEVICE_REG commands

descriptions to include information about resetting QSPI flash.

• Added new topic: Error Code Recovery.

• Added note in the Sub-Partition Table Layout (SPT Layout) stating that firmware doesn't read the SPT for non-HPS RSU

operations.

•

Revised step 2 in the Command Sequence To Perform Quad SPI Operations. You must issue the QSPI_SET_CS* command

regardless of the configuration scheme.

•

Revised CONF_DONE and INIT_DONE topic.

• Corrected minor errors and spelling mistakes.

2020.10.27 20.3 Made the following changes:

•

Updated QSPI_WRITE and QSPI_READ descriptions in the Command List and Description table. The text specifies that the

maximum transfer size is 4 kilobytes or 1024 words.

• Updated note in the Adding an Application Image. The note states: When using HPS to manage RSU, you must update

both copies of the Configuration Pointer Block (CBP0 and CBP1) and the sub-partition table (SPT). In a non-HPS case,

while updates to the pointer blocks are mandatory, the updates to the sub-partition table are not required.

2020.10.05 20.3 Made the following changes:

• Updated the Additional Clock Requirement for HPS, PCIe, eSRAM, and HBM2 section.

—

Added HPS_OSC_CLK clock in the FPGA Configuration topic.

— Added new topic: HPS First Configuration.

•

Globally corrected the AS_nCSO pin name.

•

Globally removed dual-purpose text from the MSEL pin description. After power on reset, the MSEL pins can be repurposed

as chip select pins. However, you cannot reuse the MSEL pins for other purpose.

• Added note on using the Parallel Flash Loader to program multiple QSPI flash devices in the IP for Use with the Avalon-ST

Configuration Scheme: Intel FPGA Parallel Flash Loader II IP Core: Functional Description section.

• Corrected I/O voltage standard in the Debugging Guidelines for the Avalon-ST Configuration Scheme section. The I/O

Bank 3A supports 1.2 V, not 1.8V.

•

Removed outdated note specific to the MSEL pins from the Avalon-ST Single-Device Configuration section.

continued...

9. Document Revision History for the Intel Agilex Configuration User Guide

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

223

Loading...

Loading...