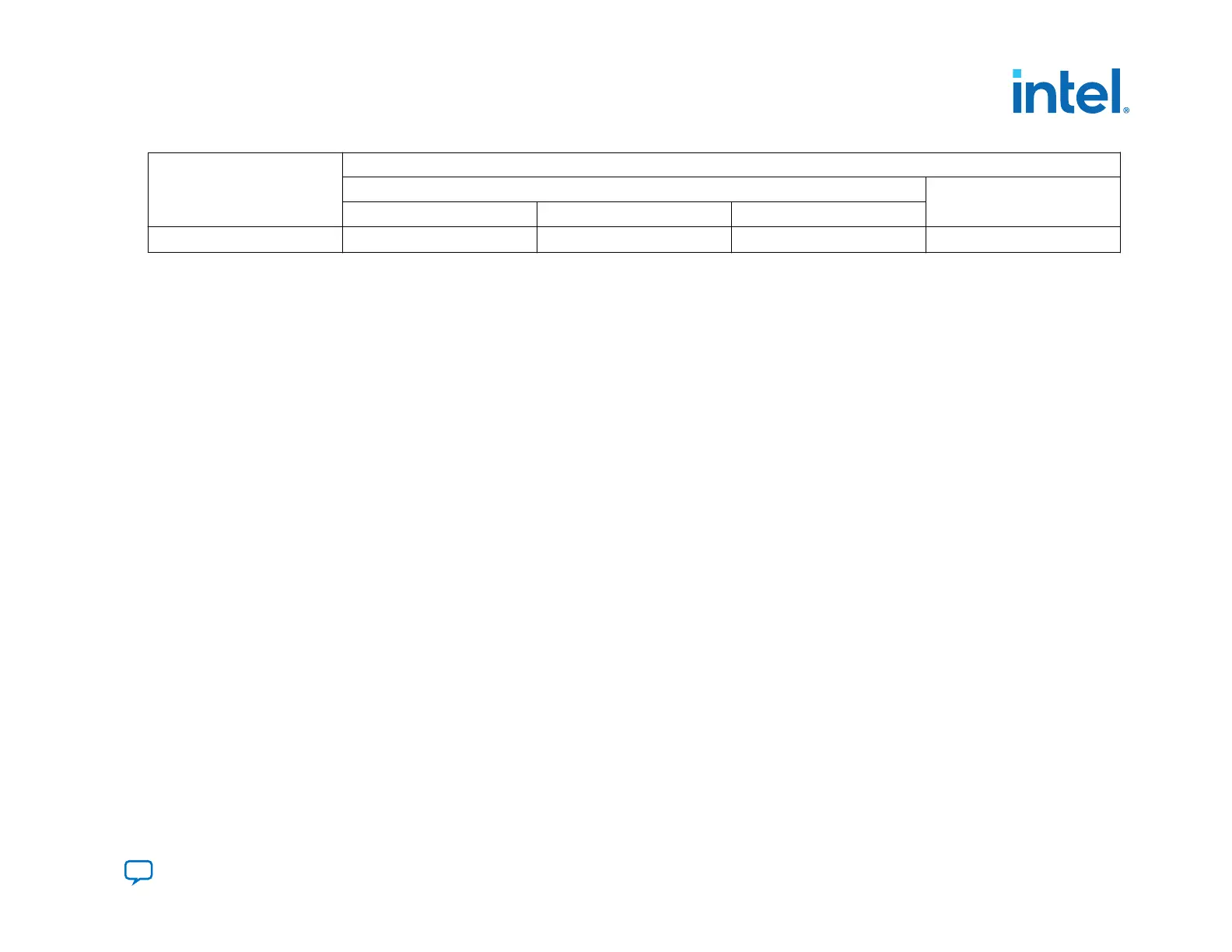

Signal Names

Configuration Scheme

Avalon-ST AS x4

x8 x16 x32

SDM_IO16 SDM_IO16

Note:

Intel recommends that you assign the CONF_DONE and INIT_DONE pins to SDM I/O pins 0 or 16. These pins have weak

internal pull-downs resistors. If you cannot use these pins, Intel recommends that you include external 4.7-kΩ pull-down

resistors to avoid false signaling.

Related Information

Intel Agilex Power Management User Guide

For more information about PWRMGT_SCL, PWRMGT_SDA, and PWRMGT_ALERT signals.

2.5.3.1. Specifying Optional Configuration Pins

You enable and assign the SDM I/O pins using the Intel Quartus Prime software.

Complete the following steps to assign these additional configuration pins:

1. On the Assignments menu, click Device.

2. In the Device and Pin Options dialog box, select the Configuration category and click Configuration Pins Options.

3. In the Configuration Pin window, enable and assign the configuration pin that you want to include in your design.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

35

Loading...

Loading...