Pin Type Weak Pull-Up Function

flash_nreset

Output — Connects to the reset pin of the flash memory device. A low signal resets

the flash memory device.

fpga_nconfig

Open Drain Output 10-kW Pull-Up

Resistor

Connects to the nCONFIG pin of the FPGA. A low pulse resets the FPGA

and initiates configuration. These pins are not available for the flash

programming option in the PFL II IP core.

(11)

pfl_reset_watchdog

Input — A switch signal to reset the watchdog timer before the watchdog timer

times out. To reset the watchdog timer hold the signal high or low for at

least two pfl_clk clock cycles.

pfl_watchdog_error

Output — When high indicates an error condition to the watchdog timer.

Related Information

Avalon Interface Specifications

3.1.7.3. Generating the PFL II IP Core

3.1.7.3.1. Controlling Avalon-ST Configuration with PFL II IP Core

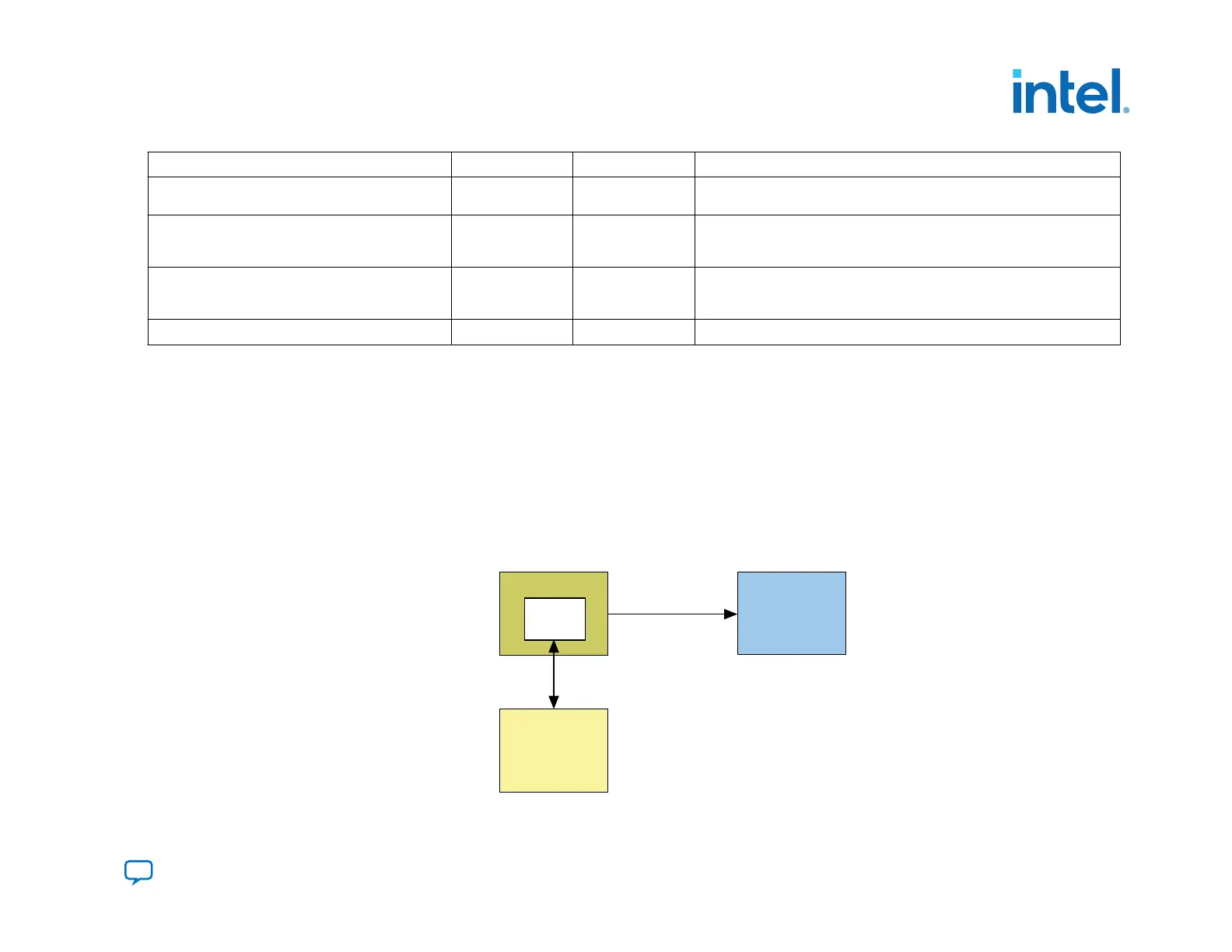

The PFL II IP core in the host determines when to start the configuration process, read the data from the flash memory

device, and configure the Intel Agilex device using the Avalon-ST configuration scheme.

Figure 27. FPGA Configuration with Flash Memory Data

Host

Flash

Memory

Intel FPGA

Flash

Interface

PFL II

Avalon-ST

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

83

Loading...

Loading...