MS51

Nov. 28, 2019 Page 340 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

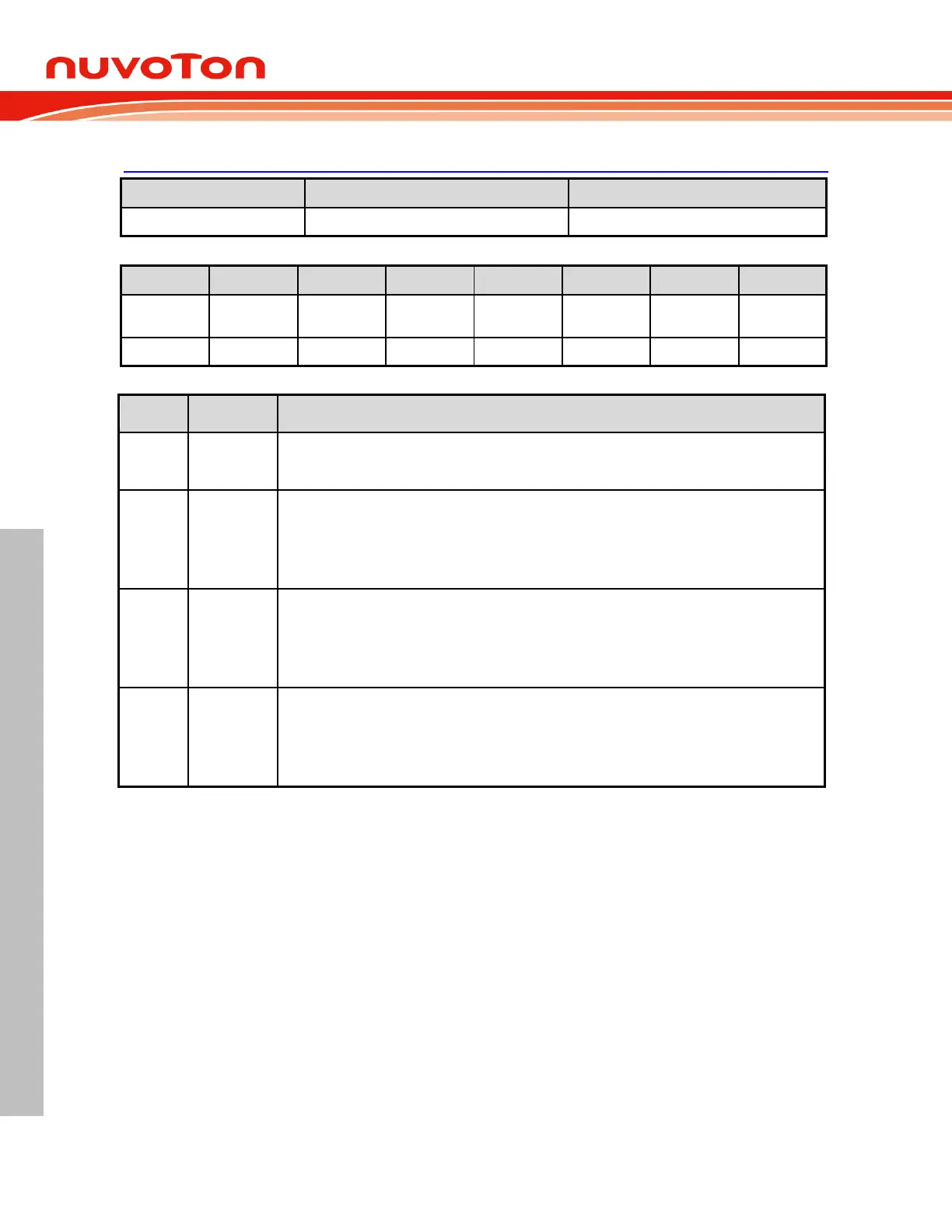

PWM0DTEN – PWM Dead-time Enable

F9H, Page 0, TA protected

PWM0 dead-time counter bit 8

See PWM0DTCNT register.

PWM0C4/5 pair dead-time insertion enable

This bit is valid only when PWM0C4/5 is under complementary mode.

0 = No delay on P0G4/P0G5 pair signals.

1 = Insert dead-time delay on the rising edge of P0G4/P0G5 pair signals.

PWM0_CH2/3 pair dead-time insertion enable

This bit is valid only when PWM0_CH2/3 is under complementary mode.

0 = No delay on P0G2/P0G3 pair signals.

1 = Insert dead-time delay on the rising edge of P0G2/P0G3 pair signals.

PWM0C0/1 pair dead-time insertion enable

This bit is valid only when PWM0C0/1 is under complementary mode.

0 = No delay on P0G0/P0G1 pair signals.

1 = Insert dead-time delay on the rising edge of P0G0/P0G1 pair signals.

Loading...

Loading...