MS51

Nov. 28, 2019 Page 401 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

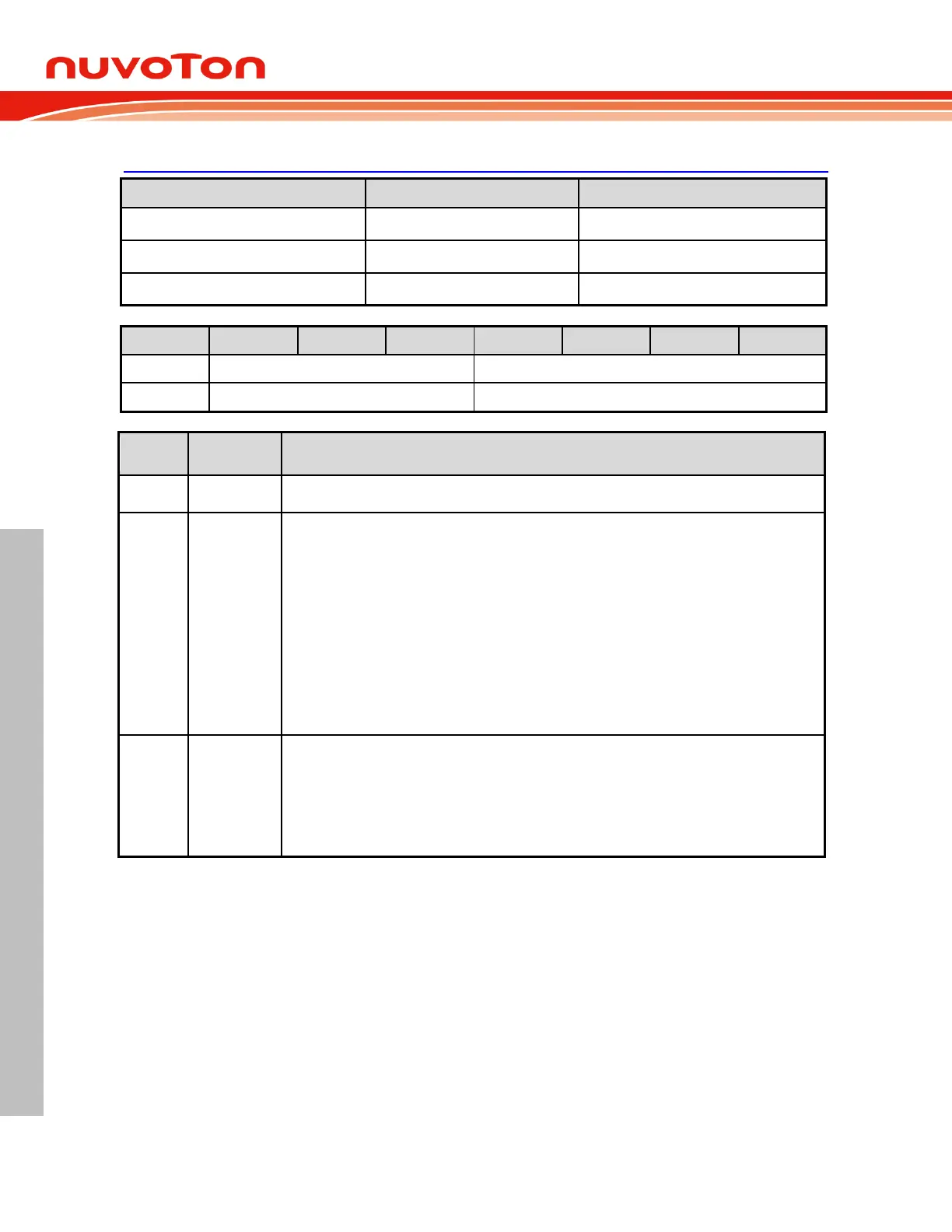

SCnETURD1 –SC ETU Rate Divider Register

SC clock divider

000 = F

SC

is F

SYS

/1.

001 = F

SC

is F

SYS

/2.

010 = F

SC

is F

SYS

/4.

011 = F

SC

is F

SYS

/8. (By default.)

100 = F

SC

is F

SYS

/16.

101 = F

SC

is F

SYS

/16.

110 = F

SC

is F

SYS

/16.

111 = F

SC

is F

SYS

/16.

Note: that the F

SC

clock should be 1Mhz ~ 5Mhz for ISO/IEC 7816-3 standard

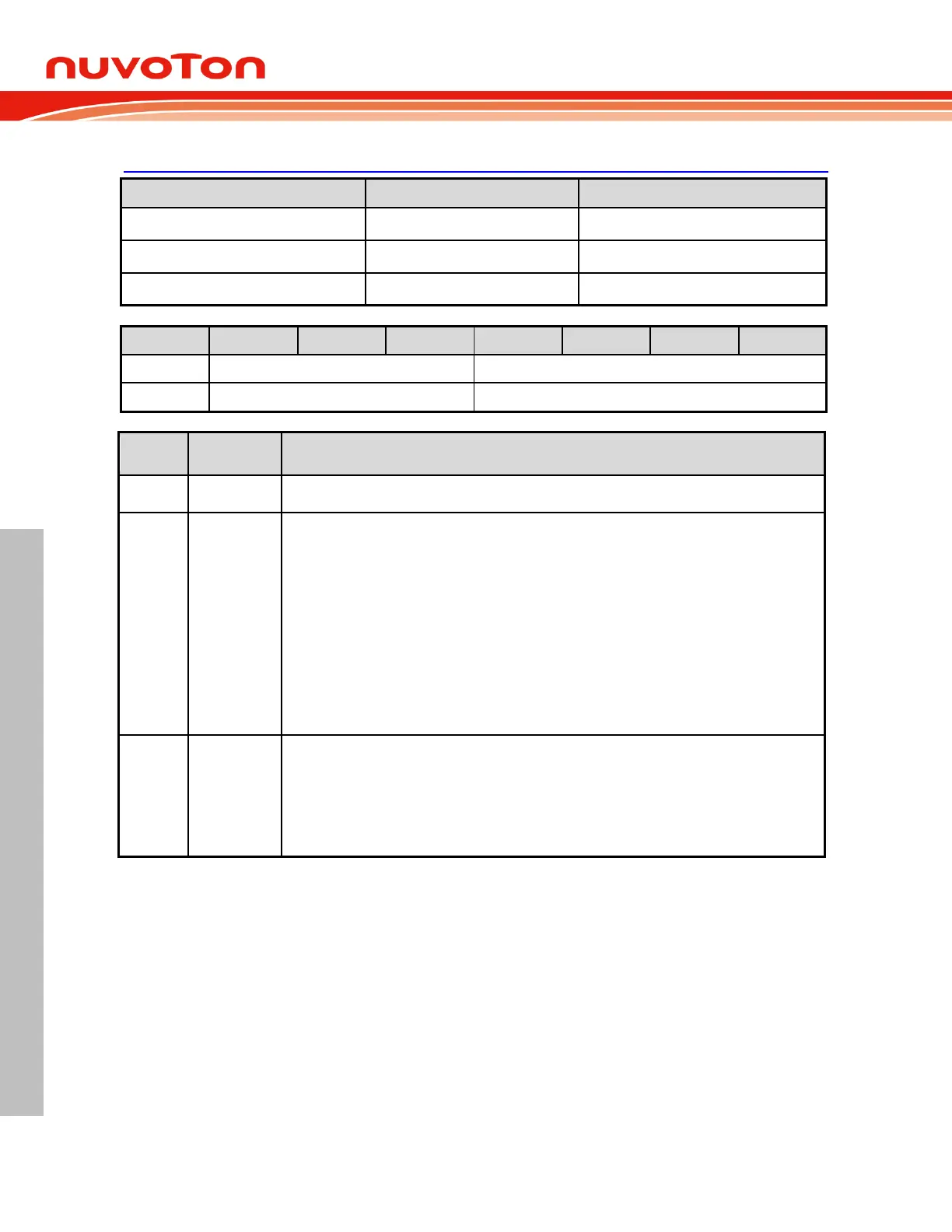

MSB bits of ETU Rate Divider

The field indicates the MSB of clock rate divider.

The real ETU is ETURDIV[11:0] + 1.

Note 1: ETURDIV[11:0] must be greater than 0x004.

Note 2: SCnETURD0 has to program first, then SCnETUDR1 .

Loading...

Loading...