Addressing

S7-300 Programmable Controller Hardware and Installation

7-10 A5E00105492-01

7.6 Consistent data

Consistent data

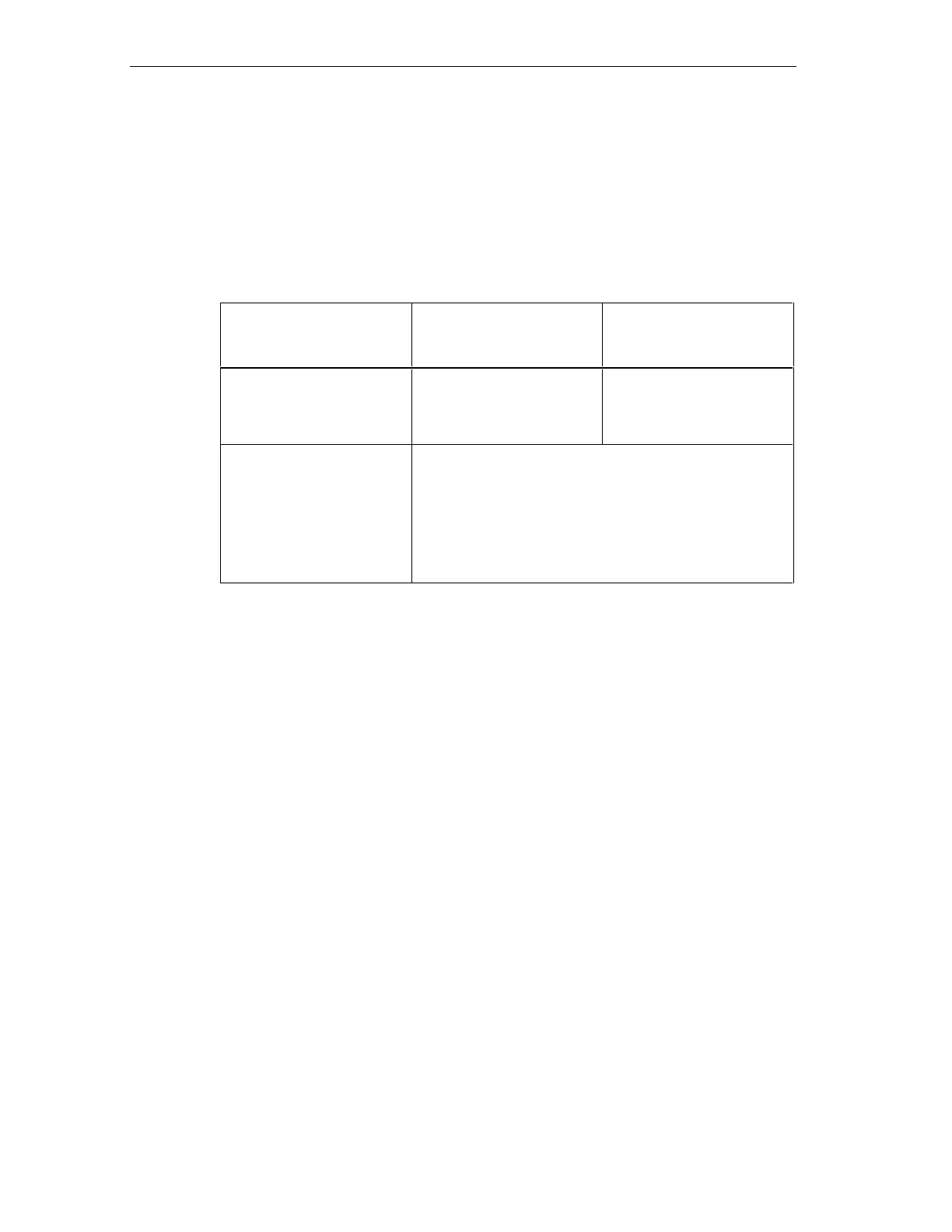

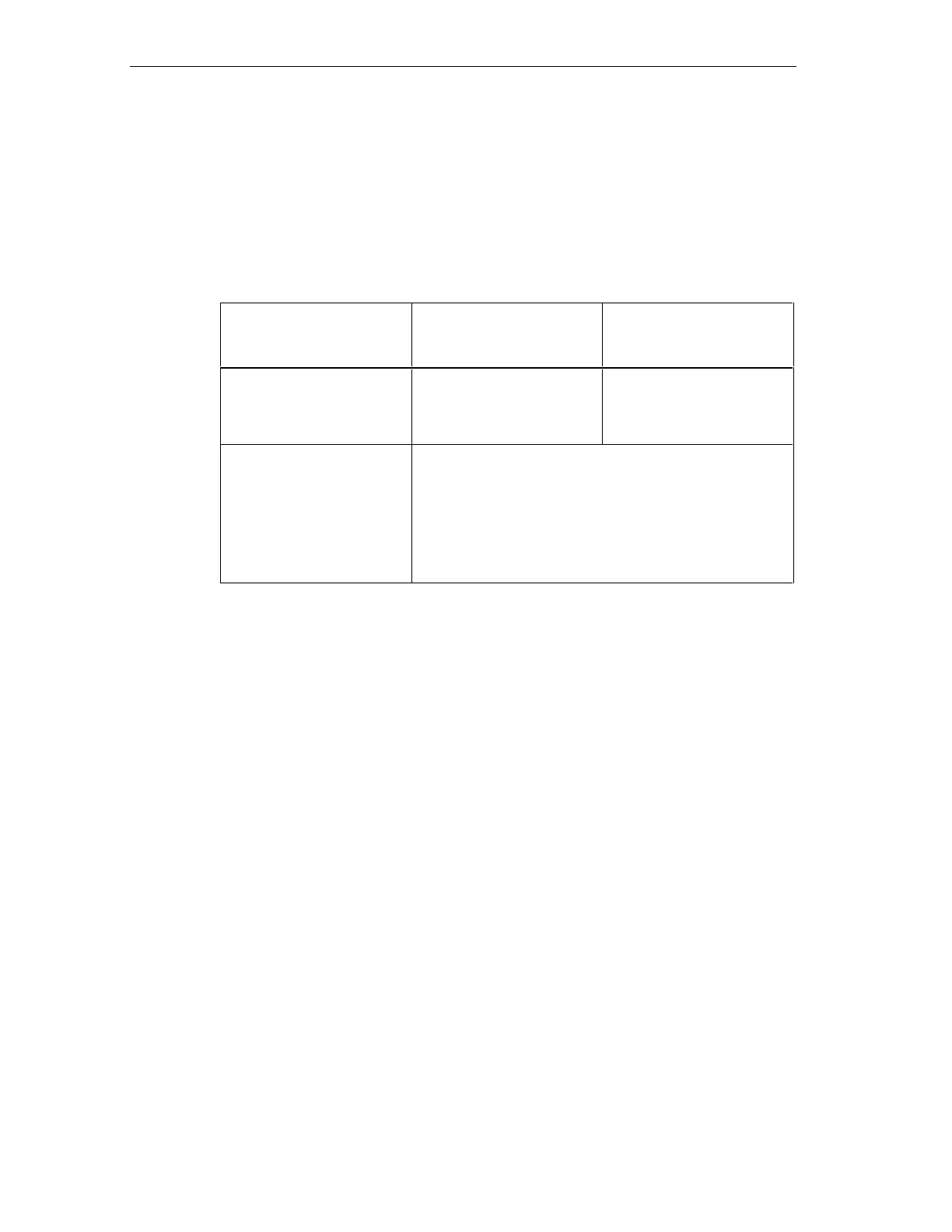

The table below shows what you have to take into account for communication in a

DP master system if you want to transfer I/O areas with "Total length" consistency.

CPUs 315-2 DP, 316-2 DP

CPU 318-2 DP

(Firmware version < V 3.0)

CPU 318-2 DP

(Firmware version≥ V 3.0)

CPUs 31xC

Even if they exist in the

process image, consistent

data is not automatically

updated.

You can choose whether or

not to update the address

area of consistent data in the

process image.

The address area of

consistent data in the

process image is

automatically updated.

To read and write consistent

data, you must use SFC14

and 15.

To read and write consistent data, you can also use SFC14

and 15.

If the address area of consistent data is not in the process

image, you must use SFC14 and 15 to read and write

consistent data.

Direct access to consistent areas is also possible (e.g.

L PEW or T PAW).

You can transfer a maximum of 32 bytes of consistent data.

Loading...

Loading...