Closed-loop thyristor current control

5-54 System- and communication configuring D7-SYS - SIMADYN D

Edition 06.2002

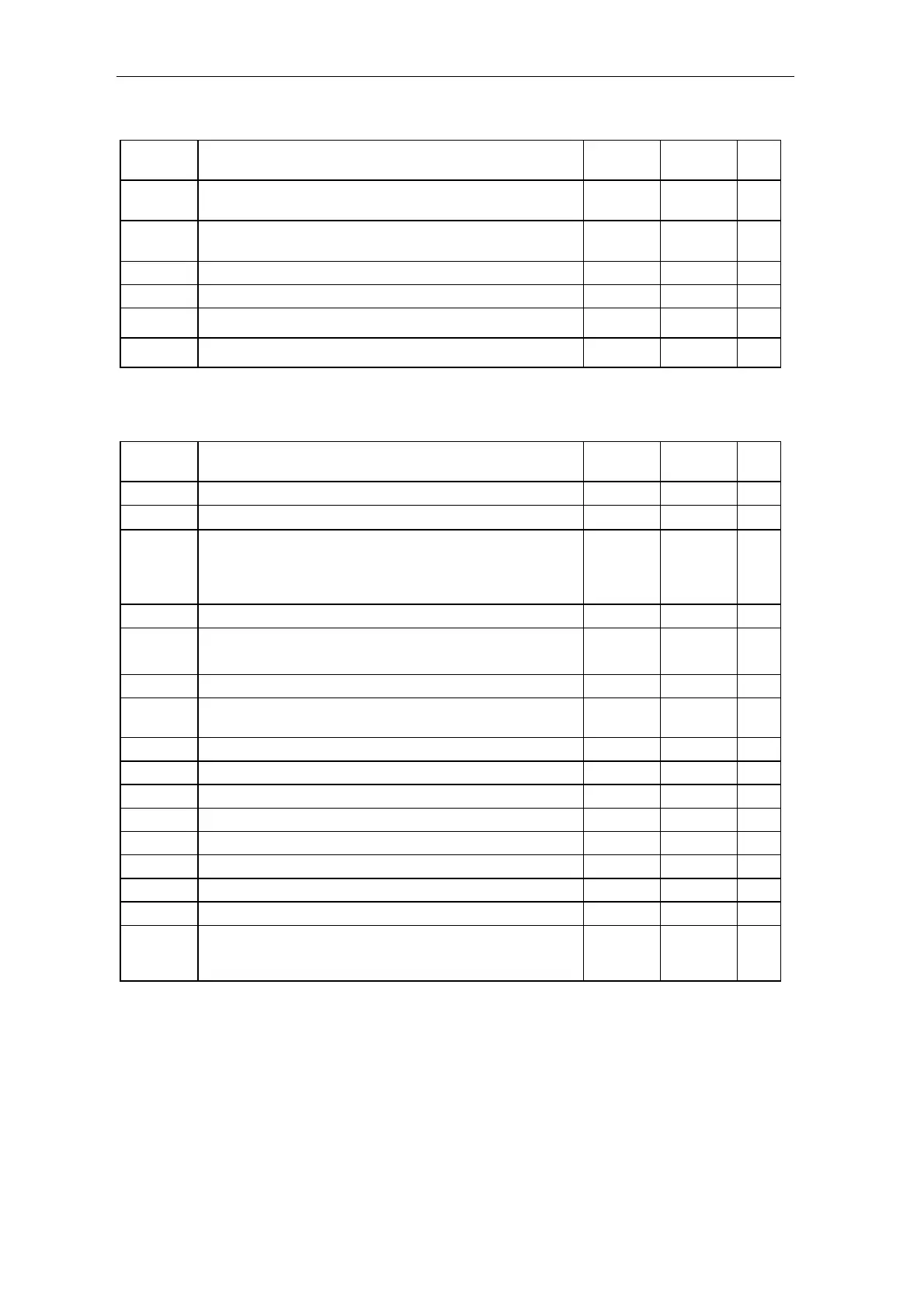

Connec-

tion

Significance Value Value

change

Type

PC6.LDU

Absolute inverter (INV) control limit [°]

Condition: 90

≤ LDU ≤ 180, > QSF\bit 9 = 1

150 Init

PC6.LDL Absolute rectifier (RECT) control limit [°]

Condition: 0

≤LDL ≤ 90, > QSF\bit 9 = 1

30 Init

PC6.DIL Tolerance of the pulse position [°]

1.0

PC6.DIZ

No. of permissible limit violations DIL 3

CSP.WCU Positive current limit (absolute value) 1.0

CSP.WCL

Negative current limit (absolute value) 1.0

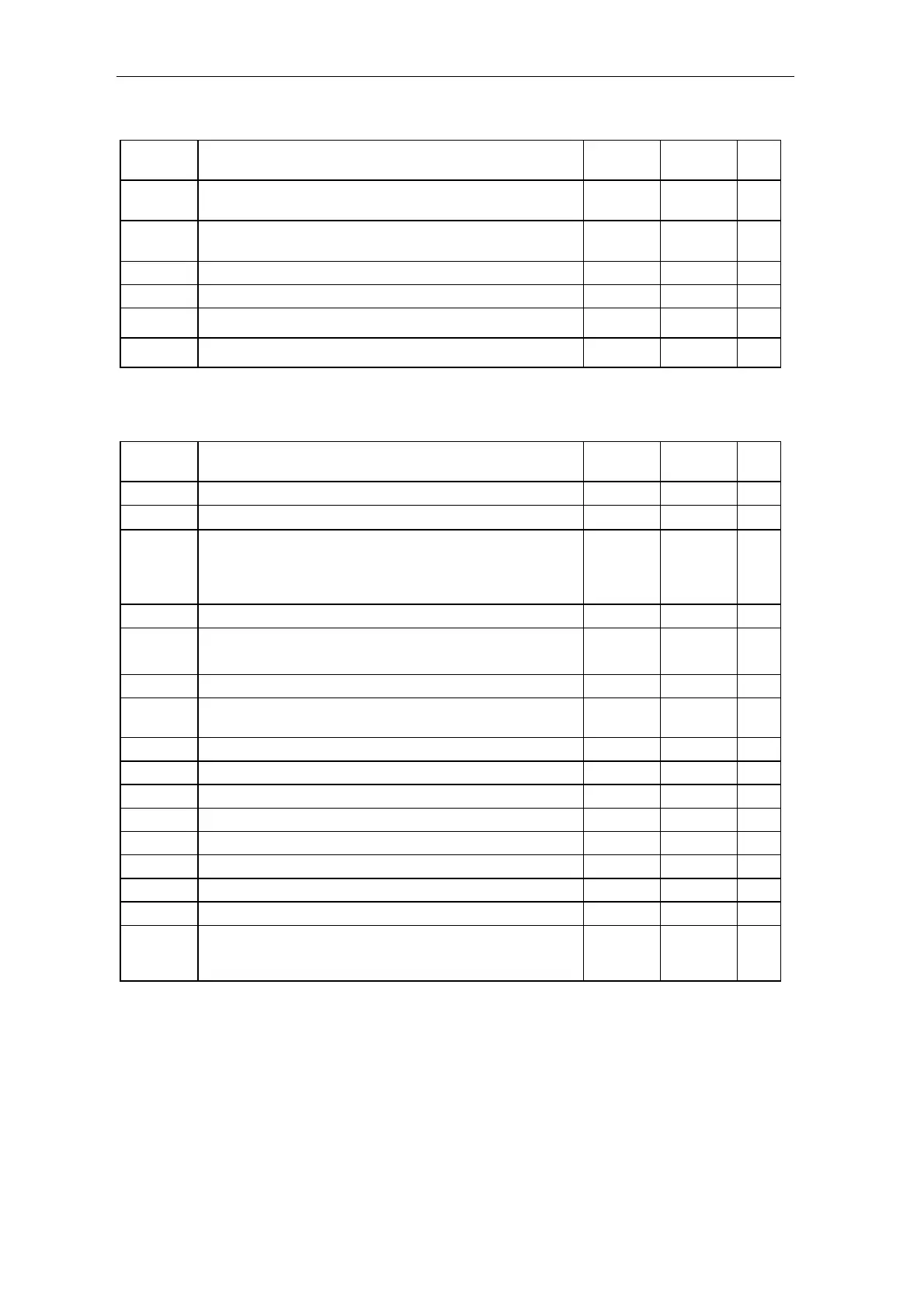

Connec-

tion

Significance Value Value

change.

Type

PA6.SYX

Mode: Synchronizing voltage source 0 Init

PA6.NCM

Mode: Line supply handling { 0…4 , >4= 0 }

0

PA6.FAM

For NCM=1: Refer to 4

For NCM=2: Average value generation {

≥1…<8 }

For NCM=3: Decrease phase difference {

≥1…≤1000 }

For NCM=4: Decrease phase step {

≥1…≤1000 }

0

PA6.INV

Mode for rotating field detection 0 Init

PA6.FNT

Line supply frequency [Hz] for the start of synchronization

Condition: 6

≤ FNT ≤ 600, > QSF\bit 9 = 1

50 Init

SOL.UNM

Mode: Handling an undervoltage condition (Sitor) 2

SOL.IEF

Mode: Use calculated EMF value

(FB EMF present )

1

SOL.NZM

Zero current signal from the SITOR set Y/N=0/1 0

SOL.OF2

Off command, torque direction M2 0

SOL.HMH

Enables the bits for the hardware signaling word YHW 16#FFFF

SOL.HM1

Enables the bits for fault word YF1 16#FFFF

SOL.HM2

Enables the bits for fault word YF2 16#FFFF

SOL.HP1

Enables the bits from YF1 for immediate pulse inhibit 16#0020

SOL.HP2

Enables the bits from YF2 for immediate pulse inhibit 16#0040

CPI.SVC

Mode: Pre-control of the CPI 0

PC6.LDP Selects the firing pulse waveform:

LDP = 0: 7kHz pulse chain,

LDP = 1: long pulses.

0Init

Selection, parameters

Loading...

Loading...