Ethernet (ETH): media access control (MAC) with DMA controller RM0008

1011/1128 DocID13902 Rev 15

• TDES1: Transmit descriptor Word1

Bit 10 NC: No carrier

When set, this bit indicates that the Carrier Sense signal form the PHY was not asserted

during transmission.

Bit 9 LCO: Late collision

When set, this bit indicates that frame transmission was aborted due to a collision occurring

after the collision window (64 byte times, including preamble, in MII mode). This bit is not

valid if the Underflow Error bit is set.

Bit 8 EC: Excessive collision

When set, this bit indicates that the transmission was aborted after 16 successive collisions

while attempting to transmit the current frame. If the RD (Disable retry) bit in the MAC

Configuration register is set, this bit is set after the first collision, and the transmission of the

frame is aborted.

Bit 7 VF: VLAN frame

When set, this bit indicates that the transmitted frame was a VLAN-type frame.

Bits 6:3 CC: Collision count

This 4-bit counter value indicates the number of collisions occurring before the frame was

transmitted. The count is not valid when the Excessive collisions bit (TDES0[8]) is set.

Bit 2 ED: Excessive deferral

When set, this bit indicates that the transmission has ended because of excessive deferral

of over 24 288 bit times if the Deferral check (DC) bit in the MAC Control register is set high.

Bit 1 UF: Underflow error

When set, this bit indicates that the MAC aborted the frame because data arrived late from

the RAM memory. Underflow error indicates that the DMA encountered an empty transmit

buffer while transmitting the frame. The transmission process enters the Suspended state

and sets both Transmit underflow (Register 5[5]) and Transmit interrupt (Register 5[0]).

Bit 0 DB: Deferred bit

When set, this bit indicates that the MAC defers before transmission because of the

presence of the carrier. This bit is valid only in Half-duplex mode.

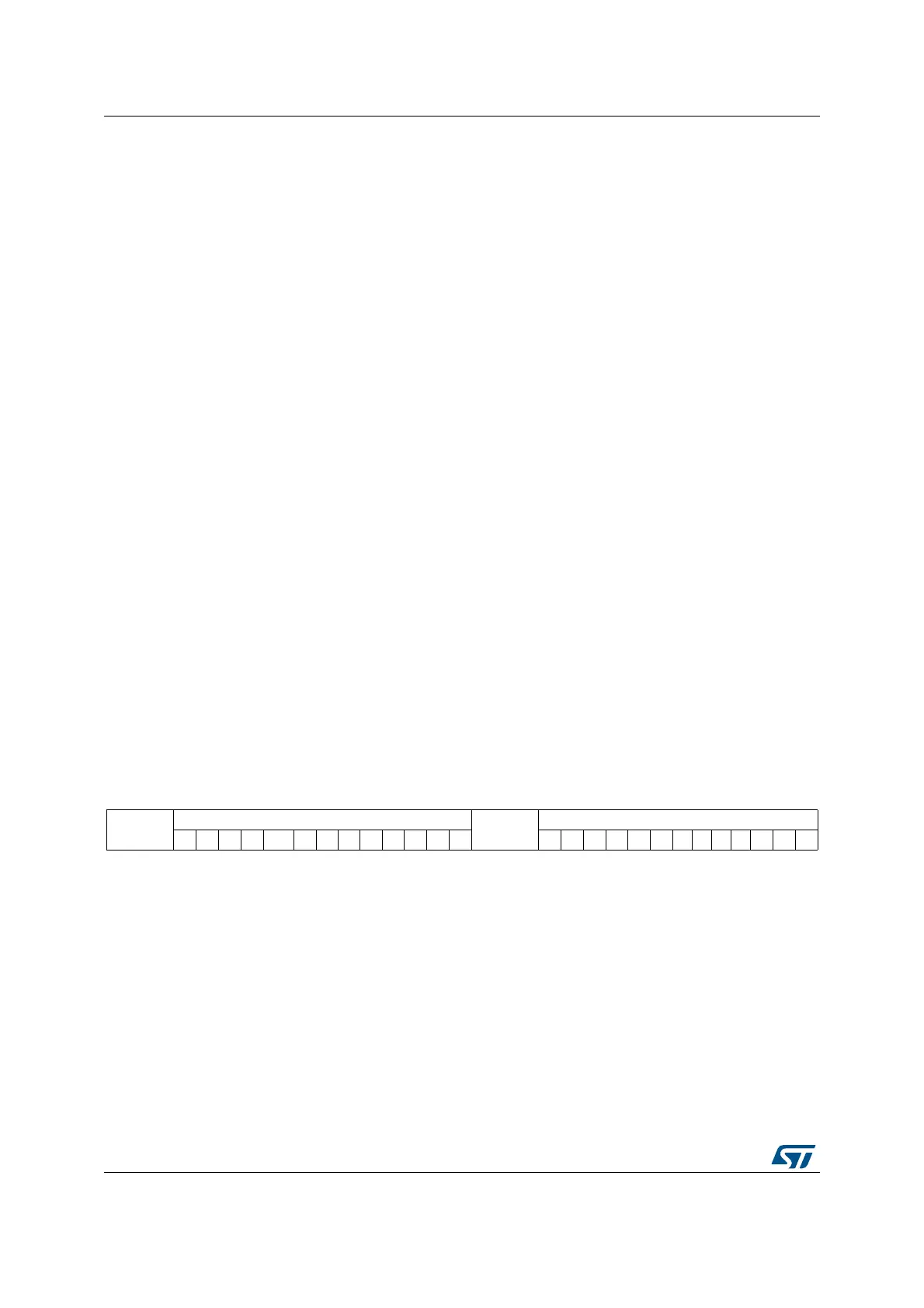

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

TBS2

Reserved

TBS1

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

31:29 Reserved, must be kept at reset value.

28:16 TBS2: Transmit buffer 2 size

These bits indicate the second data buffer size in bytes. This field is not valid if TDES0[20] is

set.

15:13 Reserved, must be kept at reset value.

12:0 TBS1: Transmit buffer 1 size

These bits indicate the first data buffer byte size, in bytes. If this field is 0, the DMA ignores

this buffer and uses Buffer 2 or the next descriptor, depending on the value of TCH

(TDES0[20]).

Loading...

Loading...