KCU116 Board User Guide 34

UG1239 (v1.2) September 28, 2018 www.xilinx.com

Chapter3: Board Component Descriptions

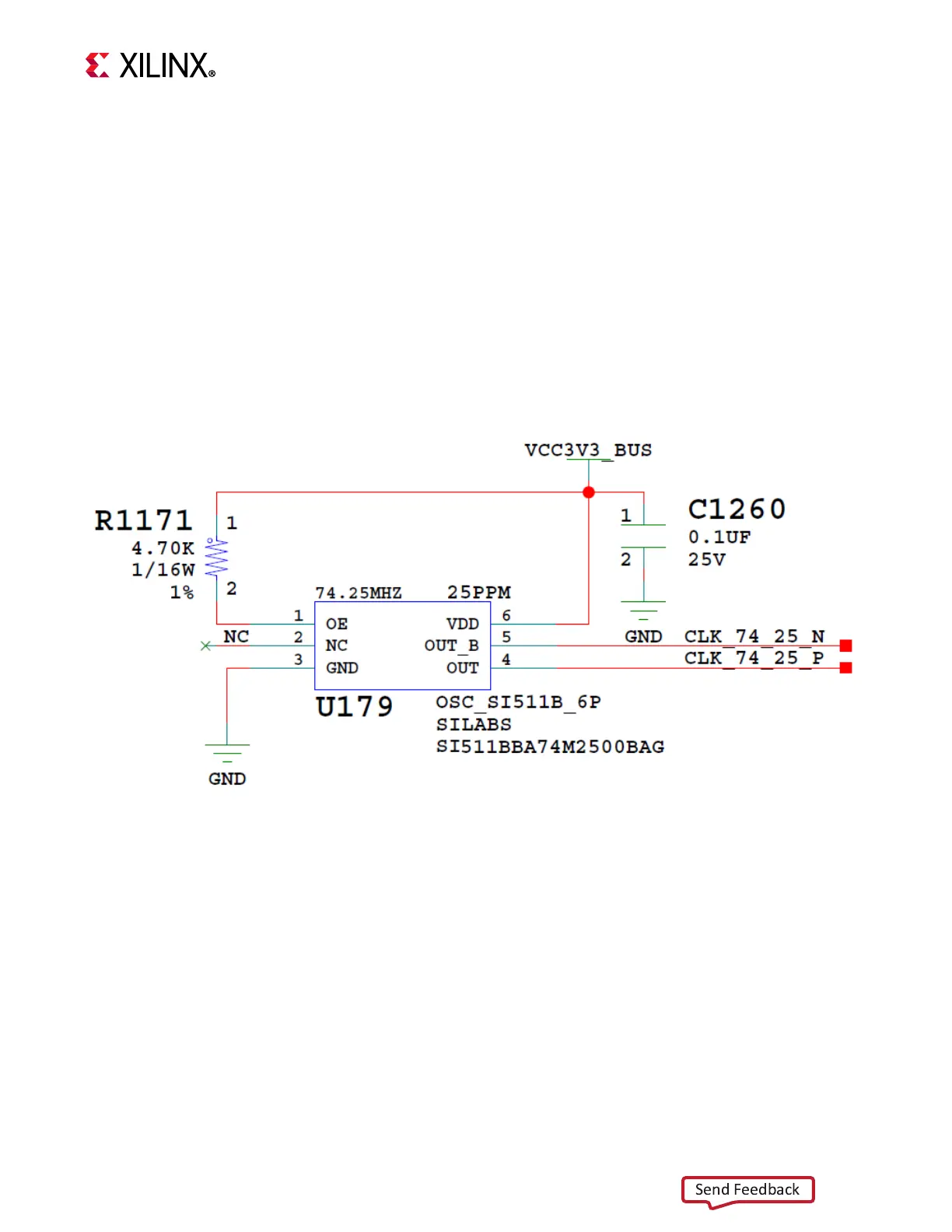

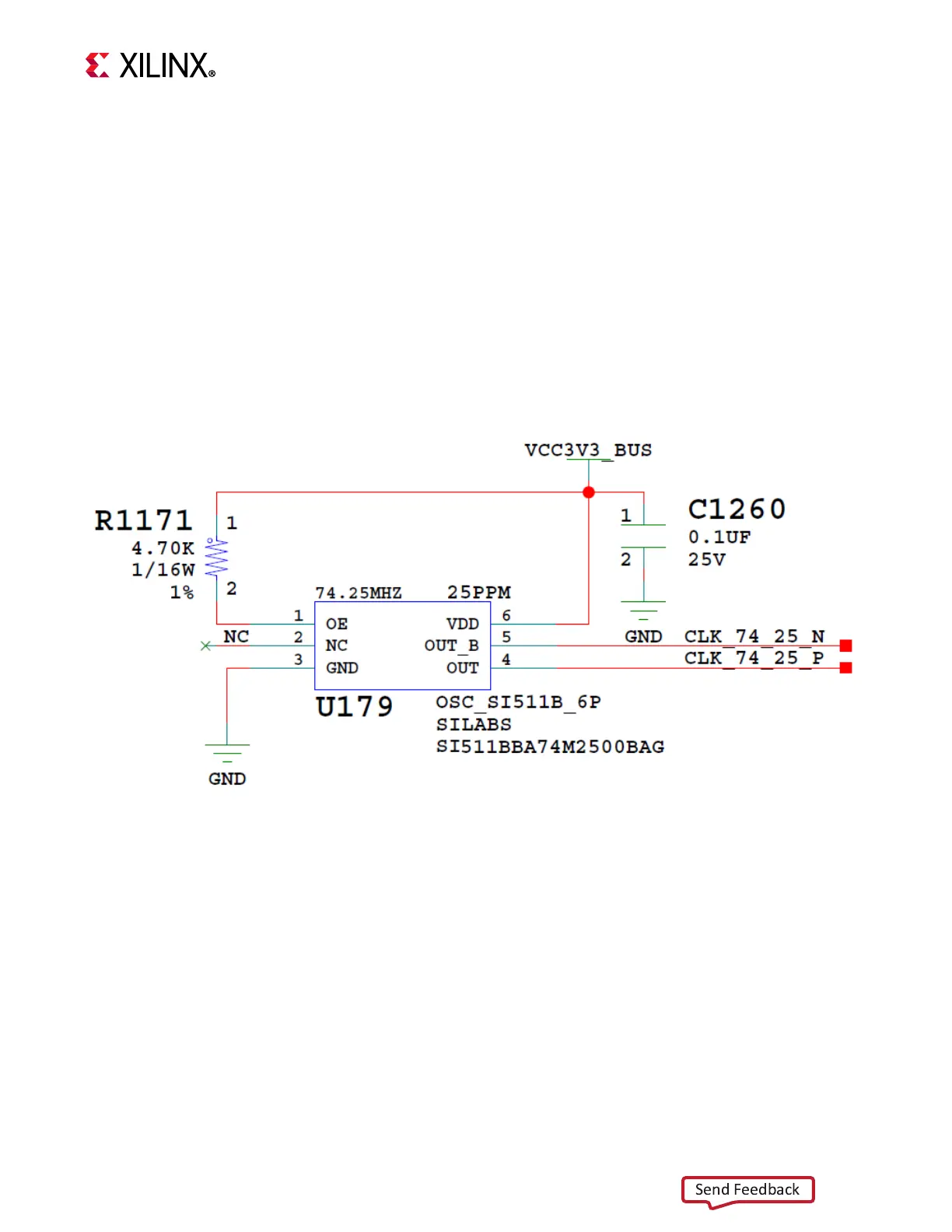

Video Clock

[Figure 2-1, near callout 6, bottom of board]

The KCU116 evaluation board has a SI511B low-jitter 3.3V LVDS fixed frequency 74.25 MHz

differential LVDS oscillator (U179) connected to the FPGA U1 bank 86 inputs pin D11 (P) and

D10 (N).

• Fixed frequency oscillator: Silicon Labs Si511BBA74M2500BAG (74.25 MHz)

• Frequency jitter: 50 ppm

• 3.3V LVDS differential output

The video clock circuit is shown in Figure 3-10.

For more details on the Silicon Labs SI5335A, SI570, SI53340, SI5328C, and SI511B devices,

see the Silicon Labs website [Ref 27].

See UltraScale Architecture Clocking Resources User Guide (UG572) [Ref 6] for UltraScale

™

FPGA clocking information.

X-Ref Target - Figure 3-10

Figure3‐10: Video Clock

Loading...

Loading...