KCU116 Board User Guide 54

UG1239 (v1.2) September 28, 2018 www.xilinx.com

Chapter3: Board Component Descriptions

Table 3-17 lists the connections between the U5 ADV7511 codec and the HDMI connector

P2.

For more information about the Analog Devices ADV7511KSTZ-P, see the Analog Devices

website [Ref 30]. For additional information about HDMI IP options, see the DisplayPort

LogiCORE Product Guide (PG064) [Ref 19].

I2C Bus

[Figure 2-1, callouts 20, 21]

The KCU116 evaluation board implements a 2-to-1 I

2

C bus arrangement. A single I

2

C bus

from each of the FPGA U1 XCKU5P (IIC_MAIN_SCL/SDA_LS) and system controller

Zynq-7000 SoC U111 (SYSCTLR_I2C_SCL/SDA) are wired to the same I

2

C bus via

level-shifters (FPGA U1 is wired through level-shifter U162 and system controller U161 is

wired through level-shifter U163). The output sides of U162 and U163 are wired in parallel

to a common I

2

C bus (IIC_SDA and _SCL_MAIN). This common I

2

C bus is then routed to a

pair of 1-to-8 channel I2C TI PCA9548 bus switches (U34 and U135) and a TI TCA6416A I2C

GPIO expander (U147). The bus switches can operate at speeds up to 400 kHz.

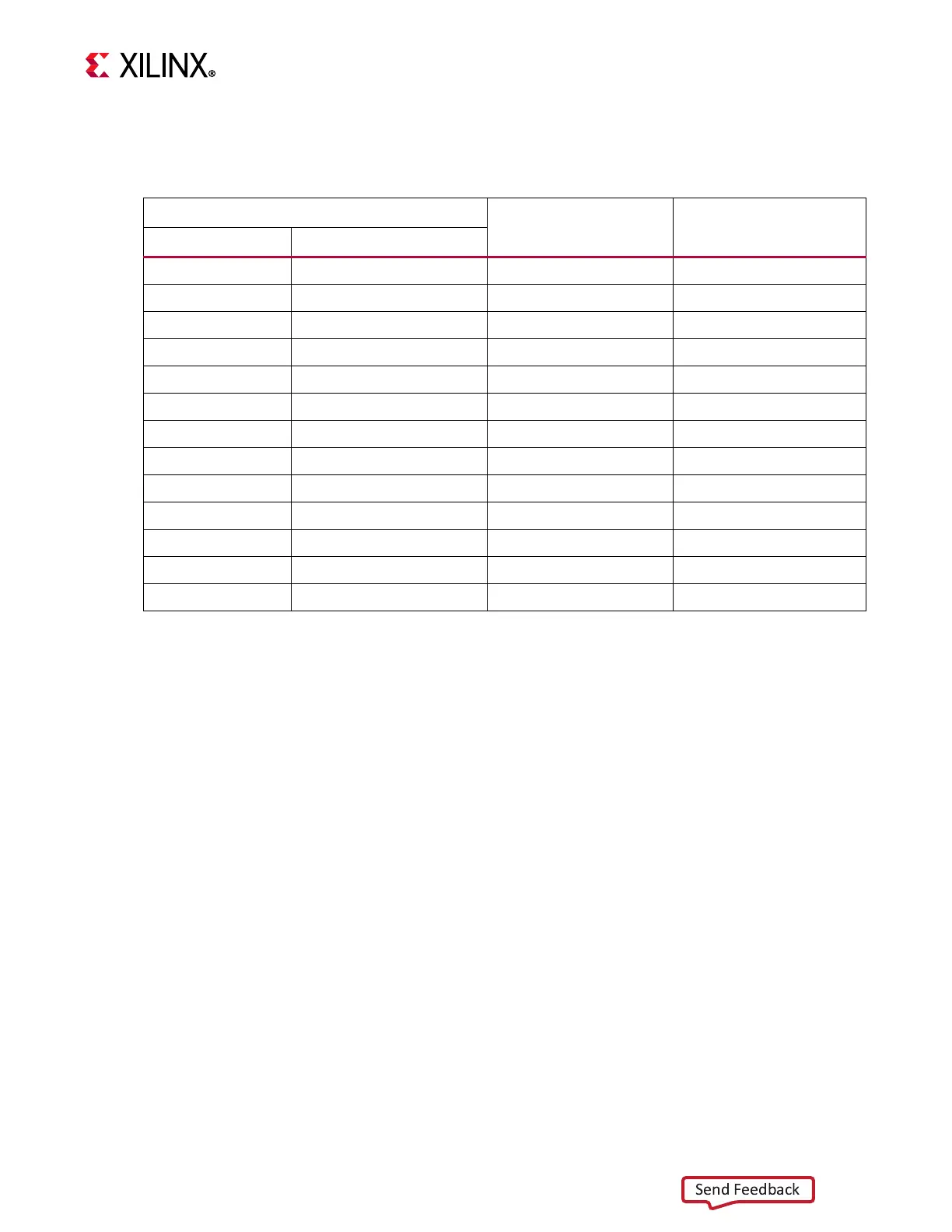

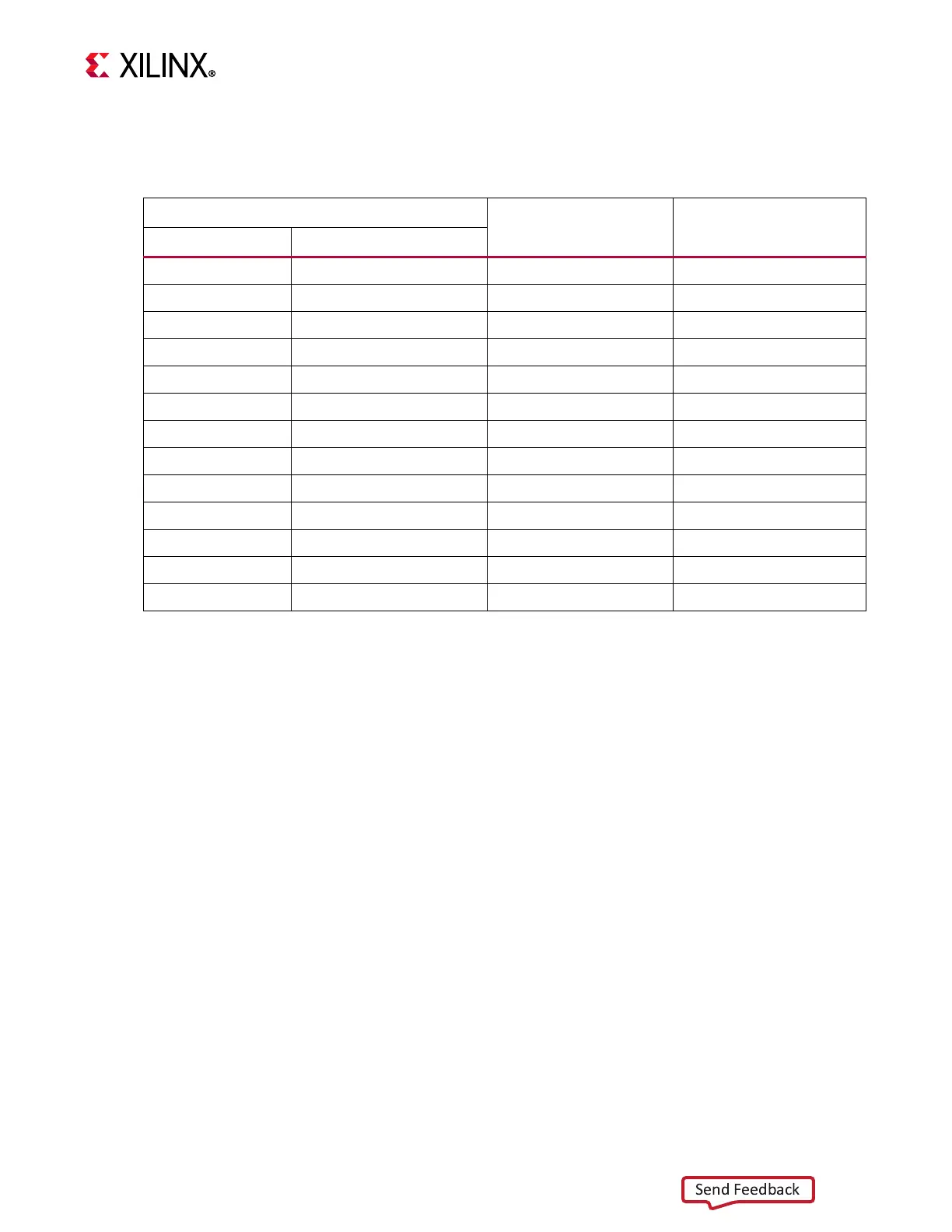

Table3‐17: HDMI ADV511 Codec U52 to P6 Connections

ADV7511 (U54)

Schematic Net Name HDMI Connector P6 Pin

Name Pin

TX0_P 36 HDMI_D0_P 7

TX0_N 35 HDMI_D0_N 9

TX1_P 40 HDMI_D1_P 4

TX1_N 39 HDMI_D1_N 6

TX2_P 43 HDMI_D2_P 1

TX2_N 42 HDMI_D2_N 3

TXC_P 33 HDMI_CLK_P 10

TXC_N 32 HDMI_CLK_N 12

DDCSDA 54 HDMI_DDCSDA 16

DDCSCL 53 HDMI_DDCSCL 15

HEAC_P 52 HDMI_HEAC_P 14

HEAC_N 51 HDMI_HEAC_N 19

CEC 48 HDMI_CEC 13

Loading...

Loading...