KCU116 Board User Guide 47

UG1239 (v1.2) September 28, 2018 www.xilinx.com

Chapter3: Board Component Descriptions

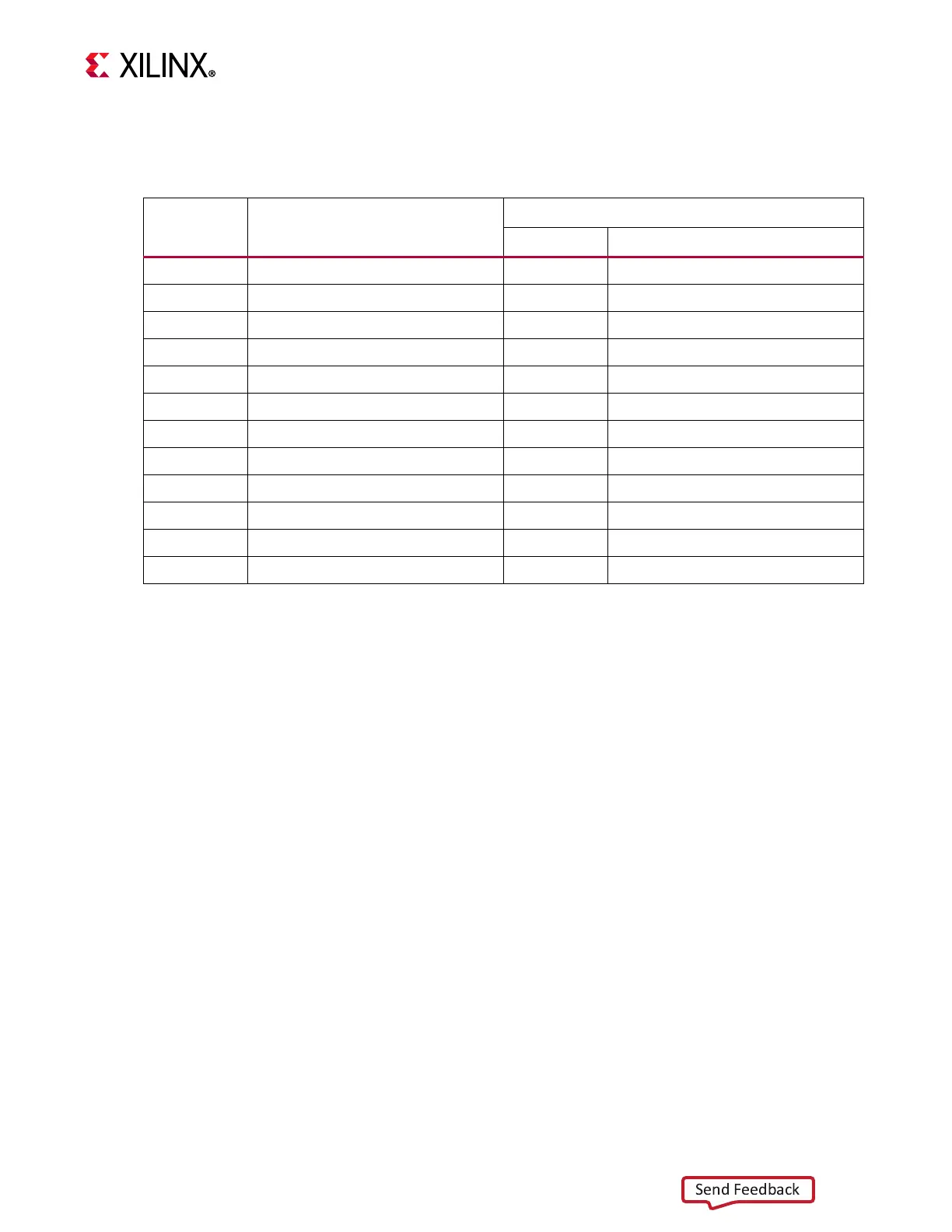

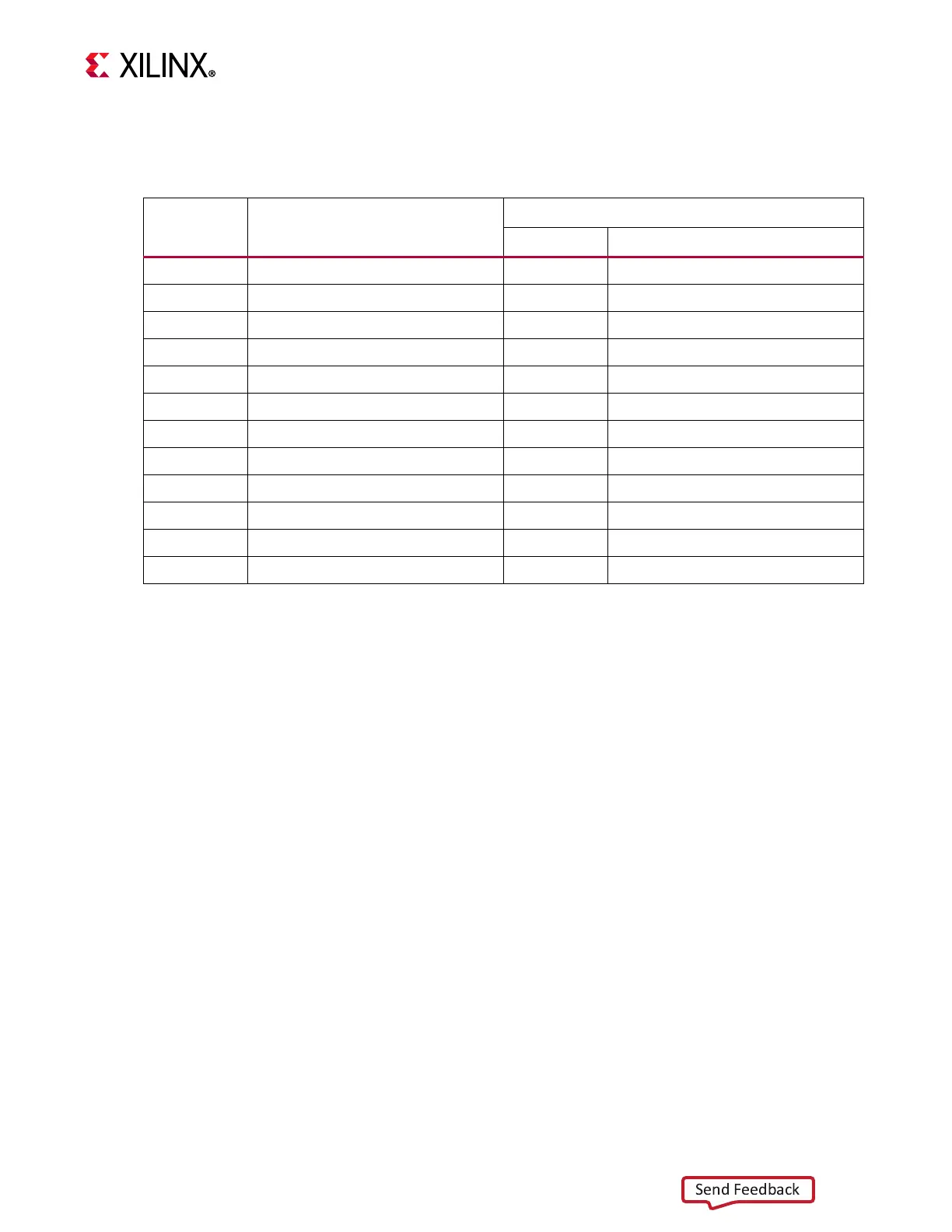

The Ethernet connections from XCKU5P FPGA U1 to the DP83867ISRGZ PHY device (U12)

are listed in Table 3-12.

Table3‐12: Ethernet Connections, XCKU5P MPSoC to the PHY Device

FPGA (U1)

Pin

Schematic Net Name

DP83867 PHY U12

Pin Name

P25 PHY1_MDIO 17 MDIO

U25 PHY1_MDC 16 MDC

R25 PHY1_PDWN_B_I_INT_B_O 44 INT_PWDN

N24 PHY1_SGMII_IN_P 27 TX_D1_SGMII_SIP

P24 PHY1_SGMII_IN_N 28 TX_D0_SGMII_SIN

U26 PHY1_SGMII_OUT_P 35 RX_D2_SGMII_SOP

V26 PHY1_SGMII_OUT_N 36 RX_D3_SGMII_SON

T24 PHY1_SGMII_CLK_P 33 RX_D0_SGMII_COP

U24 PHY1_SGMII_CLK_N 34 RX_D1_SGMII_CON

AA23 PHY1_RESET_B 43 RESET_B

T25 PHY1_CLKOUT 18 CLK_OUT

P26 PHY1_GPIO_0 39 GPIO_2

Loading...

Loading...