Model 5601MSC

Model 5601MSC Master SPG/Master Clock System

OPERATION Revision 2.2 Page - 19

2.2. GENLOCK

2.2.1. Frequency Locking

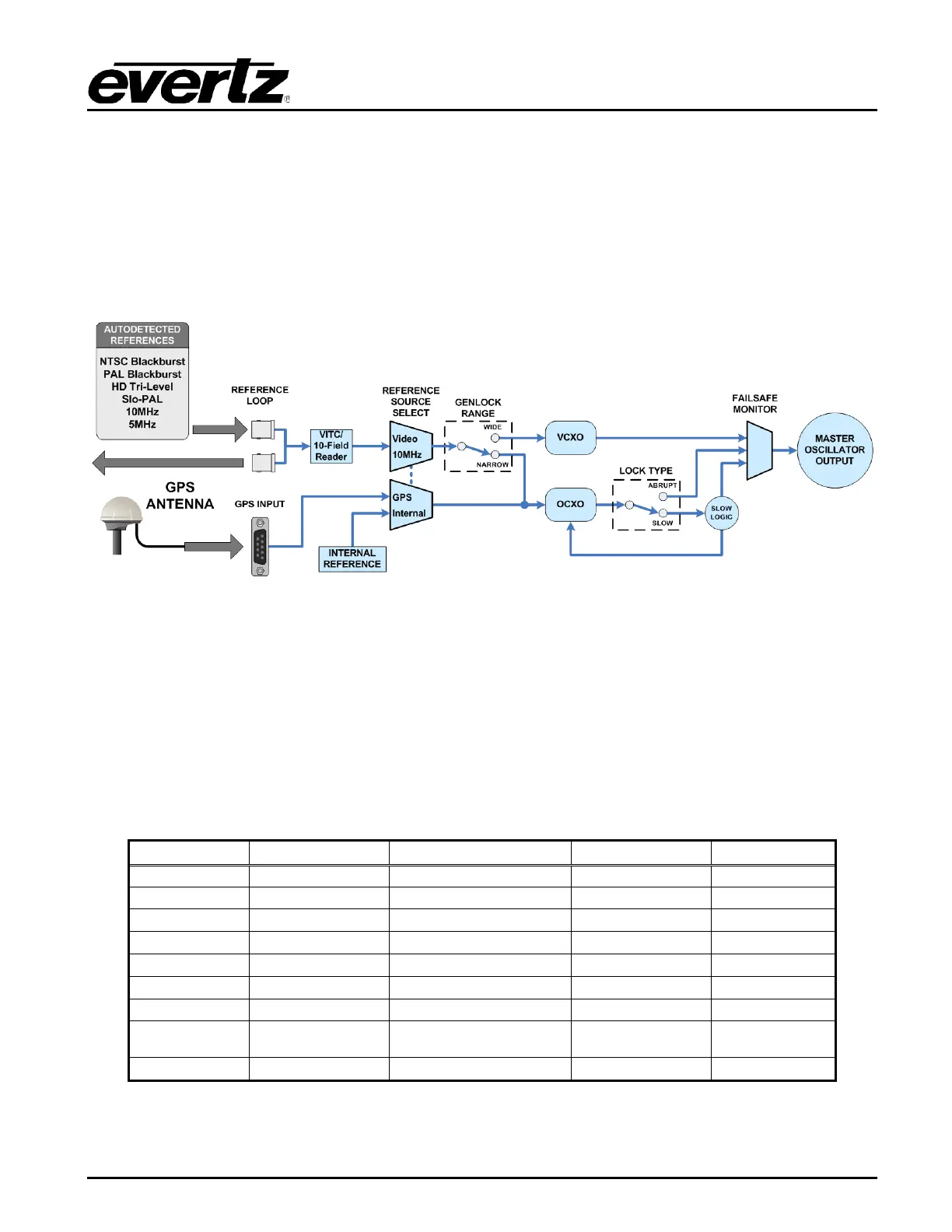

At the heart of the 5601MSC is the master oscillator circuit. Refer to the block diagram in Figure 2-6

below. For maximum versatility and reliability, two separate oscillators are employed. In narrow mode,

an ovenized quartz oscillator (OCXO) is used for maximum stability. In wide mode, a voltage controlled

oscillator (VCXO) provides a wide lock range and fast lock times. For added reliability this dual

configuration allows the unused oscillator to act as a backup to the active oscillator. In the case of a

hardware fault the backup oscillator will take over. See section 2.2.3 for more information.

Figure 2-6: Main Oscillator Circuit Block Diagram

The 5601MSC can be configured to free-run on its internal reference, or it can lock its oscillator to an

available frequency reference. This locking operation uses a Phase Lock Loop (PLL) to continuously

adjust the oscillator to track the frequency and phase of the reference signal. In narrow mode an

additional feature is available whereby the adjustment rate of the oscillator is limited to prevent sudden

changes during a re-locking operation (see Slow mode in section 2.2.4).

The 5601MSC can lock to several different frequency reference types. The supported signal types are

shown in Table 2-2. Video and Continuous Wave (CW) signals are applied to the reference loop BNCs

and are auto-detected. A GPS receiver can also be connected to the unit and used as a frequency

reference (see section 2.5). Each reference type is explained in detail in the following sections.

GPS 1pps edge

4004 PAL frames/

4800 NTSC frames

Figure 2-13 Narrow only

Table 2-2: Frequency Reference Types for the 5601MSC

Loading...

Loading...