MC68332 ELECTRICAL CHARACTERISTICS

USER’S MANUAL A-9

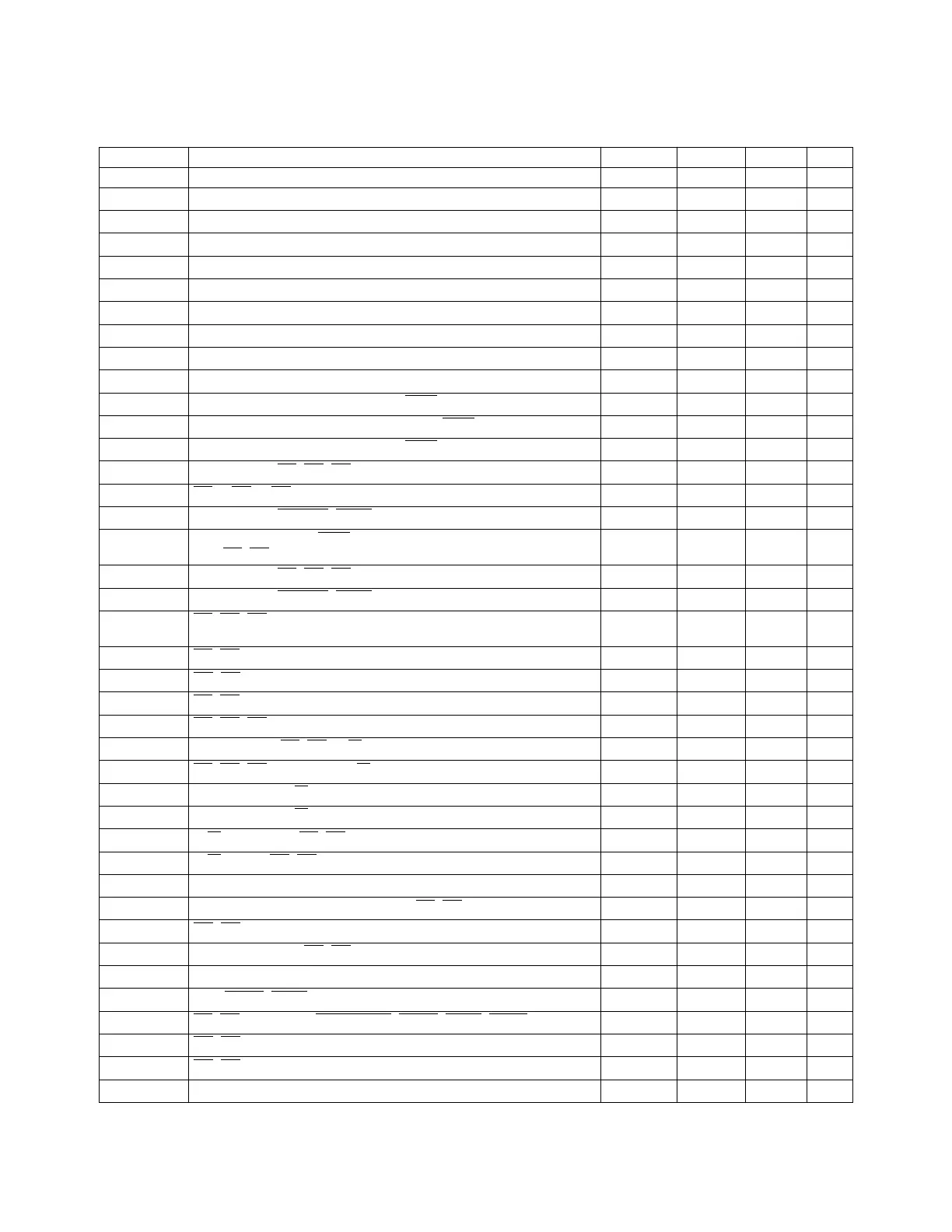

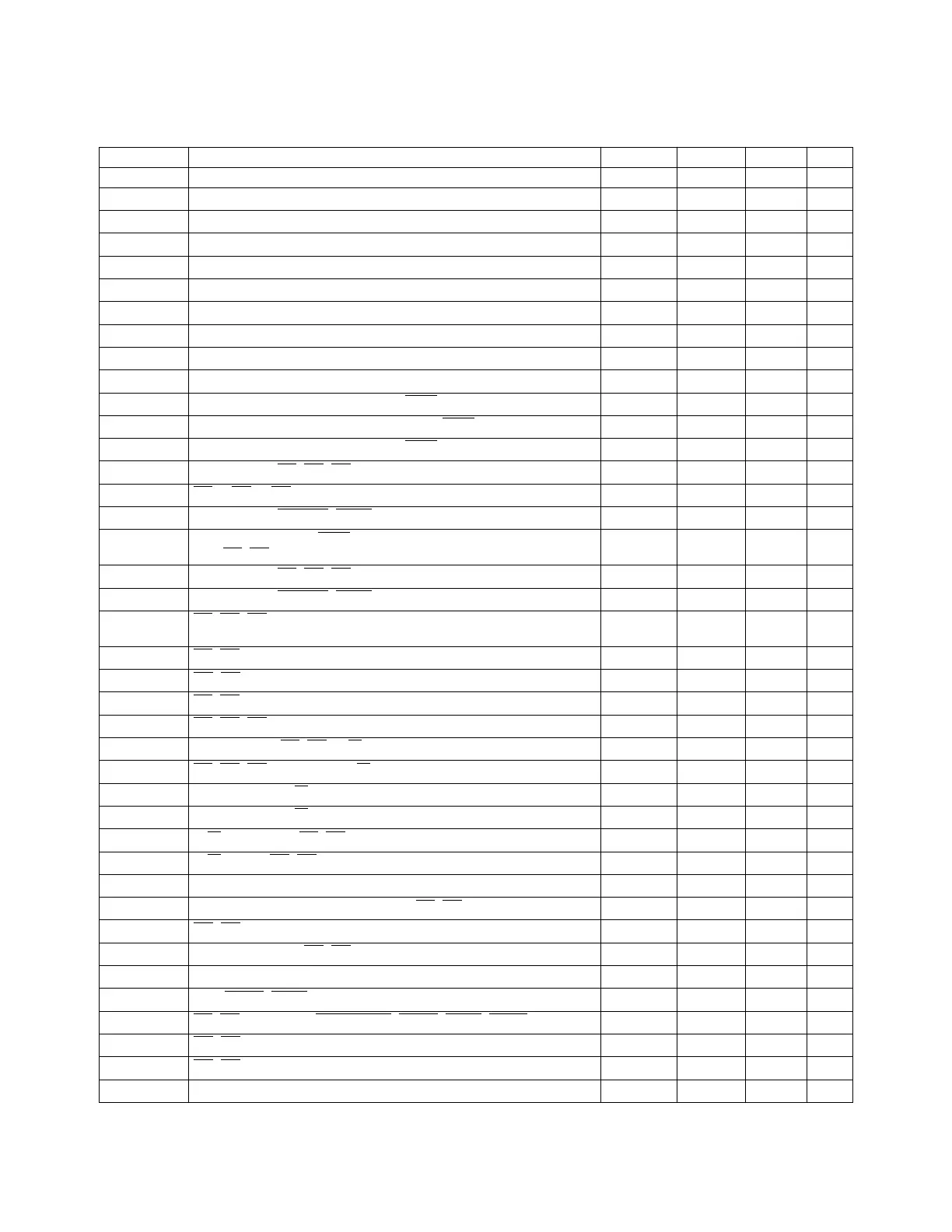

Table A-6 16.78 MHz AC Timing

(V

DD

and V

DDSYN

= 5.0 Vdc ± 10%, V

SS

= 0 Vdc, T

A

= T

L

to T

H

)

Num Characteristic Symbol Min Max Unit

F1 Frequency of Operation (32.768 kHz crystal)

2

f 0.13 16.78 MHz

1 Clock Period t

cyc

59.6 — ns

1A ECLK Period t

Ecyc

476 — ns

1B External Clock Input Period

3

t

Xcyc

59.6 — ns

2, 3 Clock Pulse Width t

CW

24 — ns

2A, 3A ECLK Pulse Width t

ECW

236 — ns

2B, 3B External Clock Input High/Low Time

3

t

XCHL

29.8 — ns

4, 5 Clock Rise and Fall Time t

Crf

—5ns

4A, 5A Rise and Fall Time — All Outputs except CLKOUT t

rf

—8ns

4B, 5B External Clock Rise and Fall Time

4

t

XCrf

—5ns

6 Clock High to Address, FC, SIZE, RMC

Valid t

CHAV

029ns

7 Clock High to Address, Data, FC, SIZE, RMC

High Impedance t

CHAZx

059ns

8 Clock High to Address, FC, SIZE, RMC

Invalid t

CHAZn

0—ns

9 Clock Low to AS

, DS, CS Asserted t

CLSA

225ns

9A AS

to DS or CS Asserted (Read)

5

t

STSA

–15 15 ns

9C Clock Low to IFETCH

, IPIPE Asserted t

CLIA

222ns

11 Address, FC, SIZE, RMC

Valid

to AS

, CS Asserted

t

AVSA

15 — ns

12 Clock Low to AS

, DS, CS Negated t

CLSN

229ns

12A Clock Low to IFETCH

, IPIPE Negated t

CLIN

222ns

13 AS

, DS, CS Negated to

Address, FC, SIZE Invalid (Address Hold)

t

SNAI

15 — ns

14 AS

, CS Width Asserted t

SWA

100 — ns

14A DS

, CS Width Asserted (Write) t

SWAW

45 — ns

14B AS

, CS Width Asserted (Fast Write Cycle) t

SWDW

40 — ns

15 AS

, DS, CS Width Negated

6

t

SN

40 — ns

16 Clock High to AS

, DS, R/W High Impedance t

CHSZ

—59ns

17 AS

, DS, CS Negated to R/W Negated t

SNRN

15 — ns

18 Clock High to R/W

High t

CHRH

029ns

20 Clock High to R/W

Low t

CHRL

029ns

21 R/W

Asserted to AS, CS Asserted t

RAAA

15 — ns

22 R/W

Low to DS, CS Asserted (Write) t

RASA

70 — ns

23 Clock High to Data Out Valid t

CHDO

—29ns

24 Data Out Valid to Negating Edge of AS

, CS t

DVASN

15 — ns

25 DS

, CS Negated to Data Out Invalid (Data Out Hold) t

SNDOI

15 — ns

26 Data Out Valid to DS

, CS Asserted (Write) t

DVSA

15 — ns

27 Data In Valid to Clock Low (Data Setup) t

DICL

5—ns

27A Late BERR

, HALT Asserted to Clock Low (Setup Time) t

BELCL

20 — ns

28 AS

, DS Negated to DSACK[1:0], BERR, HALT, AVEC Negated t

SNDN

080ns

29 DS

, CS Negated to Data In Invalid (Data In Hold)

7

t

SNDI

0—ns

29A DS

, CS Negated to Data In High Impedance

7, 8

t

SHDI

—55ns

30 CLKOUT Low to Data In Invalid (Fast Cycle Hold)

7

t

CLDI

15 — ns

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...