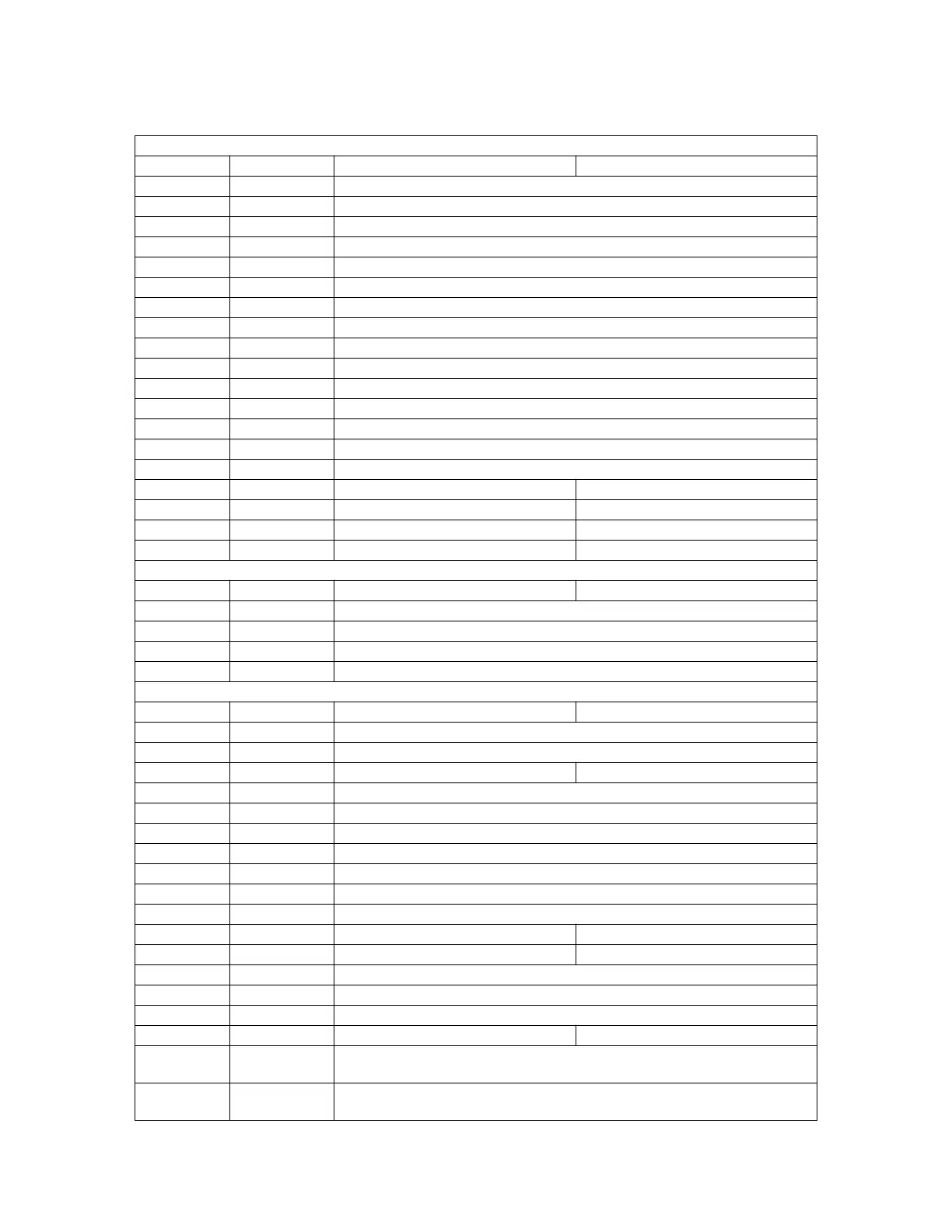

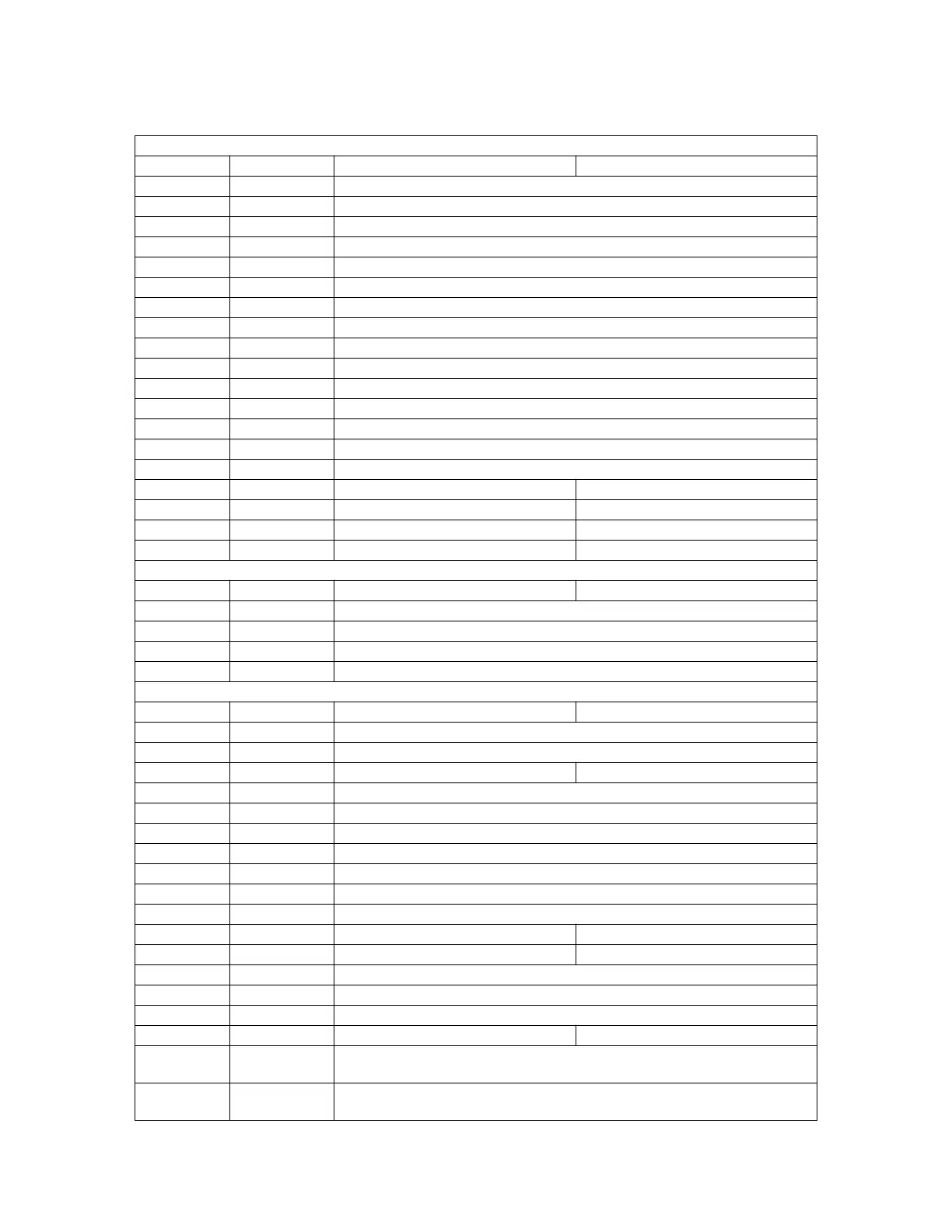

MC68332 REGISTER SUMMARY

USER’S MANUAL D-39

SIM

Access Address 15 8 7 0

S $FFFA5A CHIP-SELECT OPTION 3 (CSOR3)

S $FFFA5C CHIP-SELECT BASE 4 (CSBAR4)

S $FFFA5E CHIP-SELECT OPTION 4 (CSOR4)

S $FFFA60 CHIP-SELECT BASE 5 (CSBAR5)

S $FFFA62 CHIP-SELECT OPTION 5 (CSOR5)

S $FFFA64 CHIP-SELECT BASE 6 (CSBAR6)

S $FFFA66 CHIP-SELECT OPTION 6 (CSOR6)

S $FFFA68 CHIP-SELECT BASE 7 (CSBAR7)

S $FFFA6A CHIP-SELECT OPTION 7 (CSOR7)

S $FFFA6C CHIP-SELECT BASE 8 (CSBAR8)

S $FFFA6E CHIP-SELECT OPTION 8 (CSOR8)

S $FFFA70 CHIP-SELECT BASE 9 (CSBAR9)

S $FFFA72 CHIP-SELECT OPTION 9 (CSOR9)

S $FFFA74 CHIP-SELECT BASE 10 (CSBAR10)

S $FFFA76 CHIP-SELECT OPTION 10 (CSOR10)

$FFFA78 NOT USED NOT USED

$FFFA7A NOT USED NOT USED

$FFFA7C NOT USED NOT USED

$FFFA7E NOT USED NOT USED

TPURAM

Access Address 15 8 7 0

S $FFFB00 TPURAM MODULE CONFIGURATION REGISTER (TRAMMCR)

S $FFFB02 TPURAM TEST REGISTER (TRAMTST)

S $FFFB04 TPURAM BASE ADDRESS AND STATUS REGISTER (TRAMBAR)

S $FFFB06 NOT USED

QSM

Access Address 15 8 7 0

S $FFFC00 QSM MODULE CONFIGURATION (QSMCR)

S $FFFC02 QSM TEST (QTEST)

S $FFFC04 QSM INTERRUPT LEVEL (QILR) QSM INTERRUPT VECTOR (QIVR)

S/U $FFFC06 NOT USED

S/U $FFFC08 SCI CONTROL 0 (SCCR0)

S/U $FFFC0A SCI CONTROL 1 (SCCR1)

S/U $FFFC0C SCI STATUS (SCSR)

S/U $FFFC0E SCI DATA (SCDR)

S/U $FFFC10 NOT USED

S/U $FFFC12 NOT USED

S/U $FFFC14 NOT USED PQS DATA (PORTQS)

S/U $FFFC16 PQS PIN ASSIGNMENT (PQSPAR) PQS DATA DIRECTION (DDRQS)

S/U $FFFC18 SPI CONTROL 0 (SPCR0)

S/U $FFFC1A SPI CONTROL 1 (SPCR1)

S/U $FFFC1C SPI CONTROL 2 (SPCR2)

S/U $FFFC1E SPI CONTROL 3 (SPCR3) SPI STATUS (SPSR)

S/U $FFFC20–

$FFFCFF

NOT USED

S/U

QUEUE RAM

$FFFD00–

$FFFD1F

RECEIVE RAM (RR[0:F])

Table D-7 MC68332 Module Address Map (Continued)

(Assumes SIMCR MM = 1)

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...