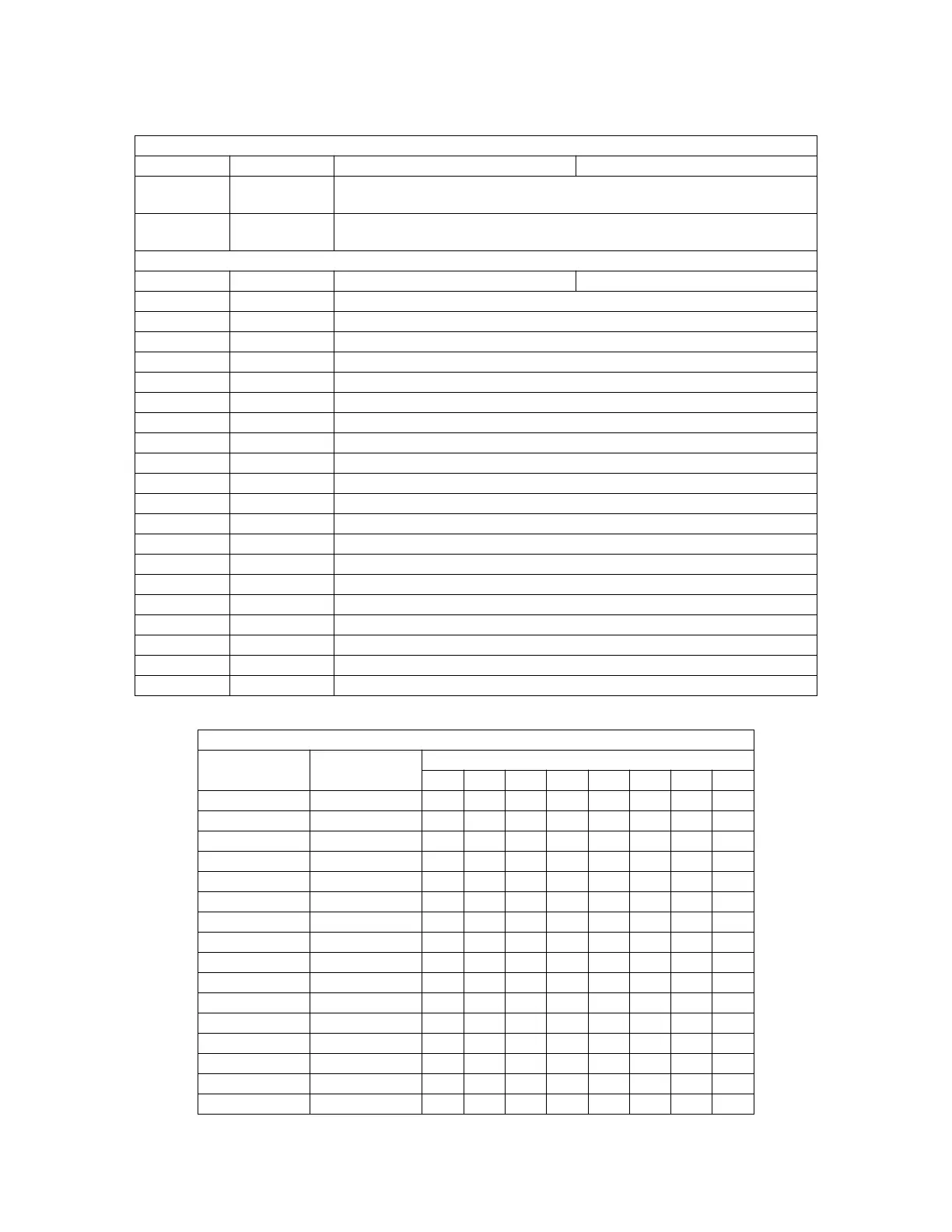

REGISTER SUMMARY MC68332

D-40 USER’S MANUAL

QSM

Access Address 15 8 7 0

S/U

QUEUE RAM

$FFFD20–

$FFFD3F

TRANSMIT RAM (TR[0:F])

S/U

QUEUE RAM

$FFFD40–

$FFFD4F

COMMAND RAM (CR[0:F])

TPU

Access Address 15 8 7 0

S $FFFE00 TPU MODULE CONFIGURATION REGISTER (TPUMCR)

S $FFFE02 TEST CONFIGURATION REGISTER (TCR)

S $FFFE04 DEVELOPMENT SUPPORT CONTROL REGISTER (DSCR)

S $FFFE06 DEVELOPMENT SUPPORT STATUS REGISTER (DSSR)

S $FFFE08 TPU INTERRUPT CONFIGURATION REGISTER (TICR)

S $FFFE0A CHANNEL INTERRUPT ENABLE REGISTER (CIER)

S $FFFE0C CHANNEL FUNCTION SELECTION REGISTER 0 (CFSR0)

S $FFFE0E CHANNEL FUNCTION SELECTION REGISTER 1 (CFSR1)

S $FFFE10 CHANNEL FUNCTION SELECTION REGISTER 2 (CFSR2)

S $FFFE12 CHANNEL FUNCTION SELECTION REGISTER 3 (CFSR3)

S/U $FFFE14 HOST SEQUENCE REGISTER 0 (HSQR0)

S/U $FFFE16 HOST SEQUENCE REGISTER 1 (HSQR1)

S/U $FFFE18 HOST SERVICE REQUEST REGISTER 0 (HSRR0)

S/U $FFFE1A HOST SERVICE REQUEST REGISTER 1 (HSRR1)

S $FFFE1C CHANNEL PRIORITY REGISTER 0 (CPR0)

S $FFFE1E CHANNEL PRIORITY REGISTER 1 (CPR1)

S $FFFE20 CHANNEL INTERRUPT STATUS REGISTER (CISR)

S $FFFE22 LINK REGISTER (LR)

S $FFFE24 SERVICE GRANT LATCH REGISTER (SGLR)

S $FFFE26 DECODED CHANNEL NUMBER REGISTER (DCNR)

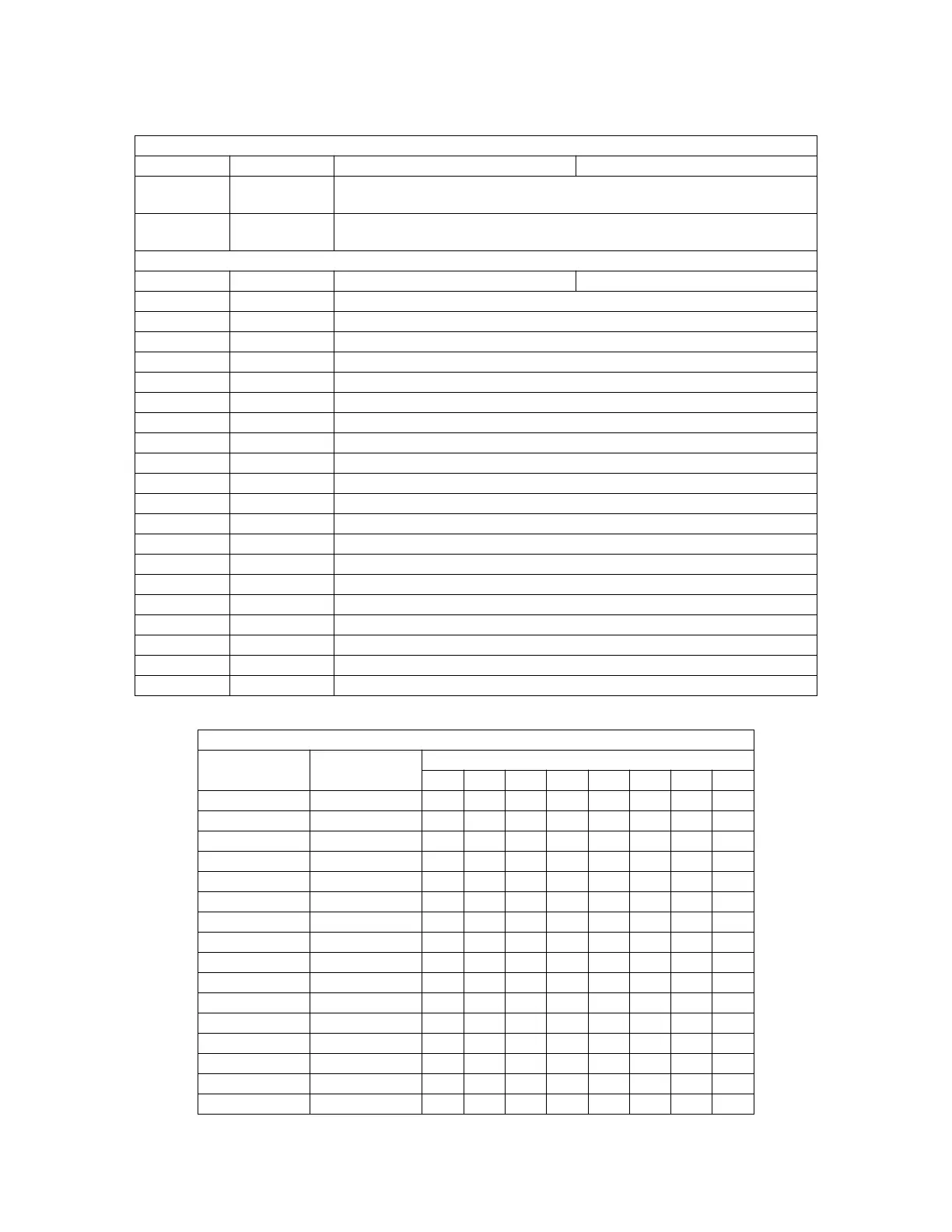

TPU Parameter RAM

Channel Base Parameter

Number Address 01234567

0 $FFFFF## 00 02 04 06 08 0A — —

1 $FFFFF## 10 12 14 16 18 1A — —

2 $FFFFF## 20 22 24 26 28 2A — —

3 $FFFFF## 30 32 34 36 38 3A — —

4 $FFFFF## 40 42 44 46 48 4A — —

5 $FFFFF## 50 52 54 56 58 5A — —

6 $FFFFF## 60 62 64 66 68 6A — —

7 $FFFFF## 70 72 74 76 78 7A — —

8 $FFFFF## 80 82 84 86 88 8A — —

9 $FFFFF## 90 92 94 96 98 9A — —

10 $FFFFF## A0 A2 A4 A6 A8 AA — —

11 $FFFFF## B0 B2 B4 B6 B8 BA — —

12 $FFFFF## C0 C2 C4 C6 C8 CA — —

13 $FFFFF## D0 D2 D4 D6 D8 DA — —

14 $FFFFF## E0 E2 E4 E6 E8 EA EC EE

15 $FFFFF## F0 F2 F4 F6 F8 FA FC FE

Table D-7 MC68332 Module Address Map (Continued)

(Assumes SIMCR MM = 1)

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...