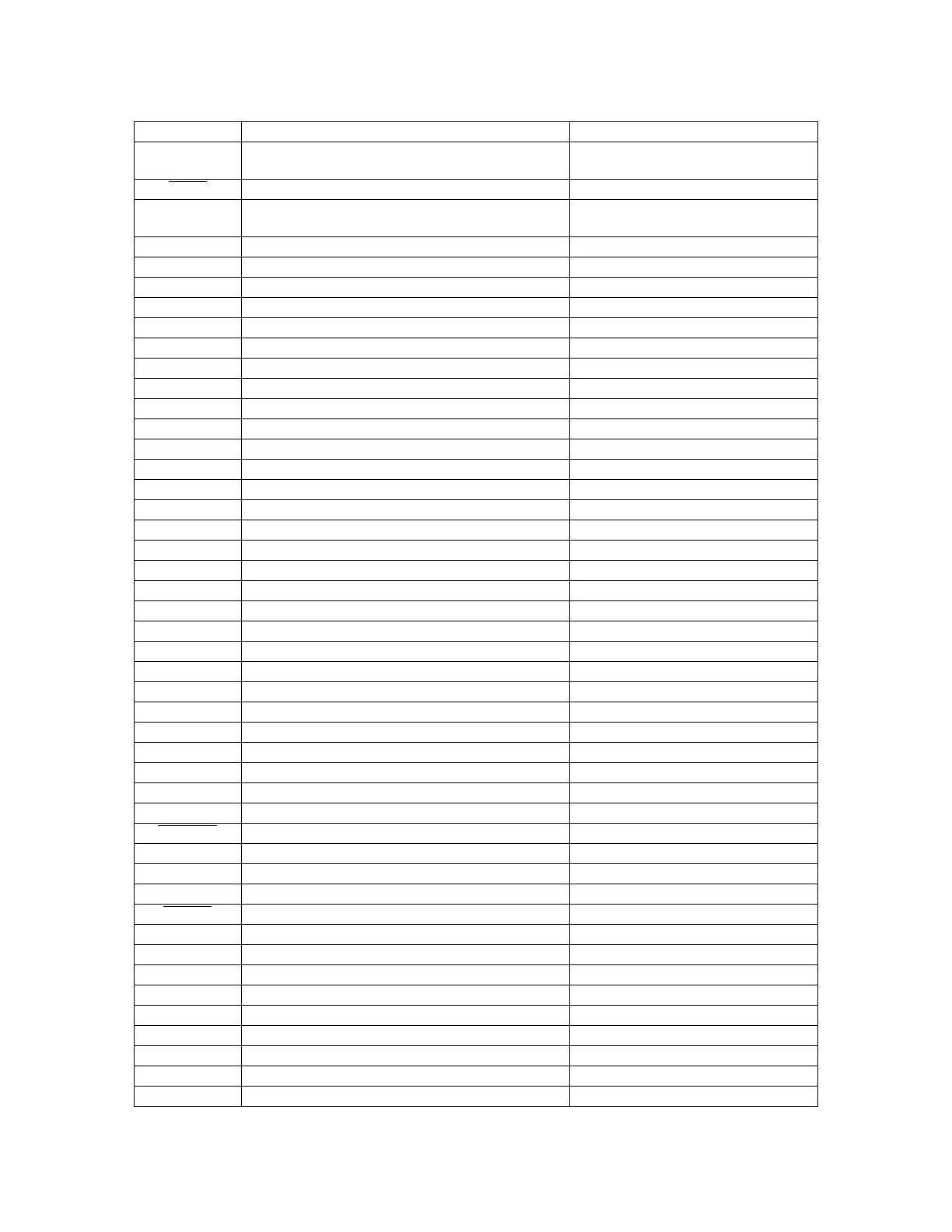

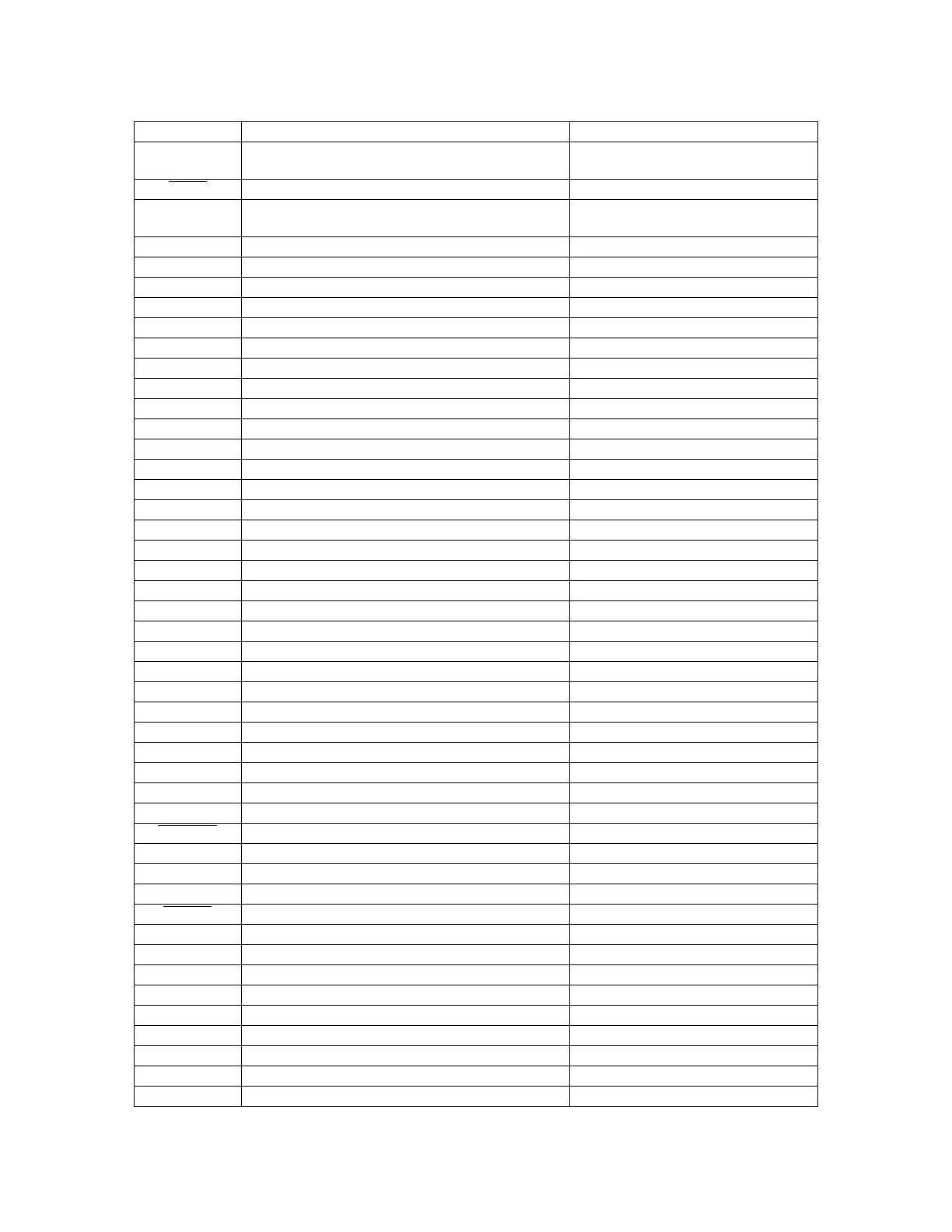

MC68332 REGISTER SUMMARY

USER’S MANUAL D-41

Table D-8 Register Bit and Field Mnemonics

Mnemonic Name Register Location

ADDR[23:11] Base Address CSBAR[0:10], CSBARBT,

TRAMBAR

AVEC

Autovector Enable CSOR[0:10], CSORBT

BP, BC, BH,

BL, BM, BT

Breakpoint Enable Points DSCR

BITS Bits Per Transfer SPCR0

BITSE Bits Per Transfer Enable CR[0:F]

BKPT Breakpoint Asserted Flag DSSR

BLC Branch Latch Control DSCR

BLKSZ Block Size CSBAR[0:10], CSBARBT

BME Bus Monitor External Enable SYPCR

BMT[1:0] Bus Monitor Timing SYPCR

BYTE Upper/Lower Byte Option CSOR[0:10], CSORBT

C Carry Flag CCR

CCL Channel Conditions Latch DSCR

CIBV Channel Interrupt Base Vector TICR

CIRL Channel Interrupt Request Level TICR

CH[15:0] Channel Function Select CFSR[0:3]

CH[15:0] Channel Interrupt Enable/Disable CIER

CH[15:0] Channel Interrupt Status CISR

CH[15:0] Channel Priority CPR[0:1]

CH[15:0] Service Status DCNR

CH[15:0] Encoded Host Sequence HSQR[0:1]

CH[15:0] Host Service Request HSRR[0:1]

CH[15:0] Link LR

CH[15:0] Service Granted SGLR

CHBK Channel Register Breakpoint Flag DSSR

CLKS Stop Clocks DSCR

CONT Continue CR[0:F]

CPHA Clock Phase SPCR0

CPOL Clock Polarity SPCR0

CPTQP Completed Queue Pointer SPSR

CSPA0[6:1] Chip-Select [6:1] CSPAR0

CSPA1[4:0] Chip-Select [4:0] CSPAR1

CSBOOT

Boot ROM Chip Select CSPAR0

DDE[7:0] Port E Data Direction DDRE

DDF[7:0] Port F Data Direction DDRF

DDQS[7:0] Port QS Data Direction DDRQS

DSACK

Data Strobe Acknowledge CSOR[0:10], CSORBT

DSCK PCS to SCK Delay CR[0:F]

DSCKL Delay Before SCK SPCR1

DT Delay After Transfer CR[0:F]

DTL Length of Delay After Transfer SPCR1

EMU Emulation Control TPUMCR

EDIV ECLK Divide Rate SYNCR

ENDQP Ending Queue Pointer SPCR2

EXOFF External Clock Off SIMCR

EXT External Reset RSR

Fr

ees

cale S

em

iconduct

or

, I

Freescale Semiconductor, Inc.

For More Information On This Product,

Go to: www.freescale.com

nc...

Loading...

Loading...