The Intel Quartus Prime Programming File Generator allows you to create many user partitions. These partitions can contain

application images and other items such as the Second Stage Boot Loader (SSBL), Linux* kernel, or Linux root file system.

When you create the initial flash image, you can create up to seven partitions for application images. There are no limitations

on creating empty partitions.

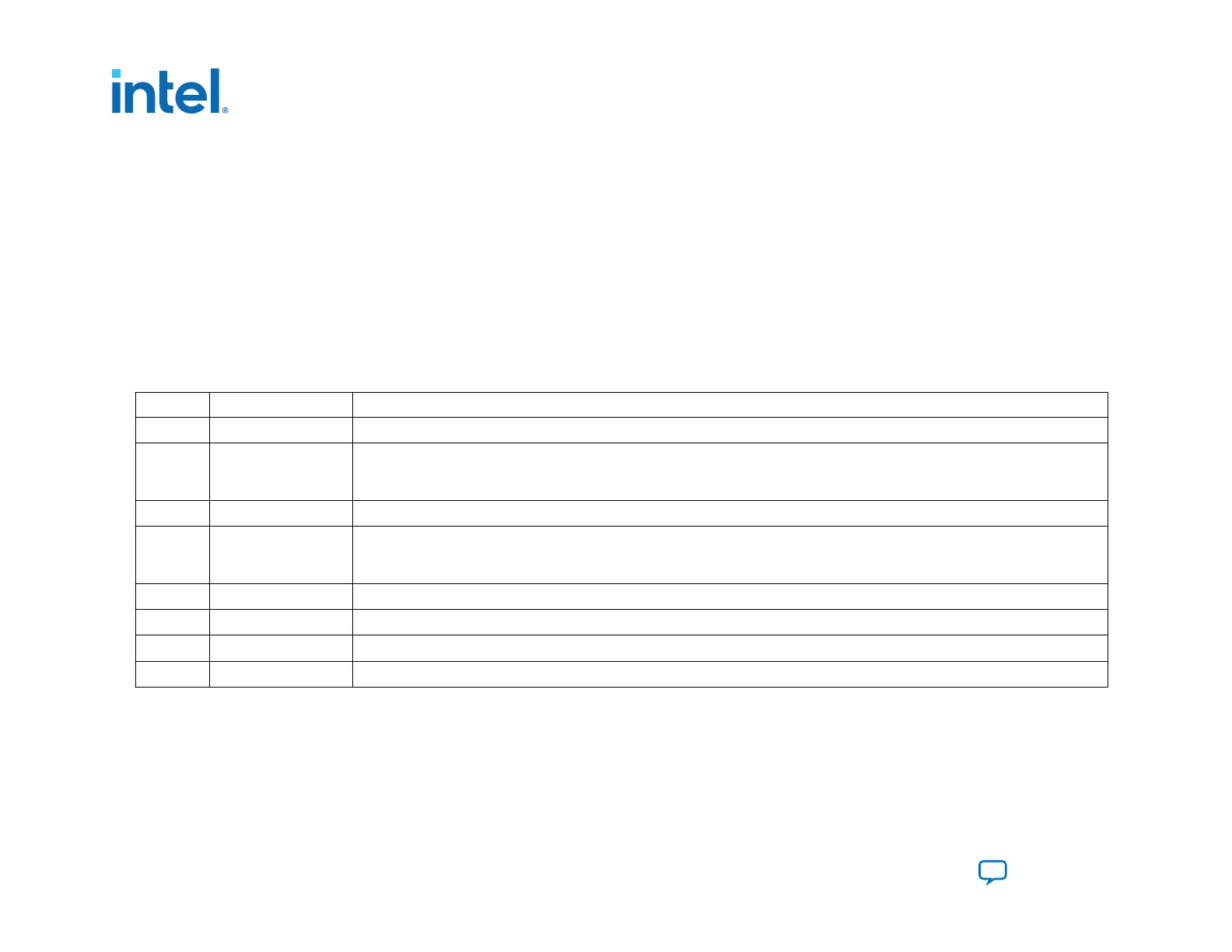

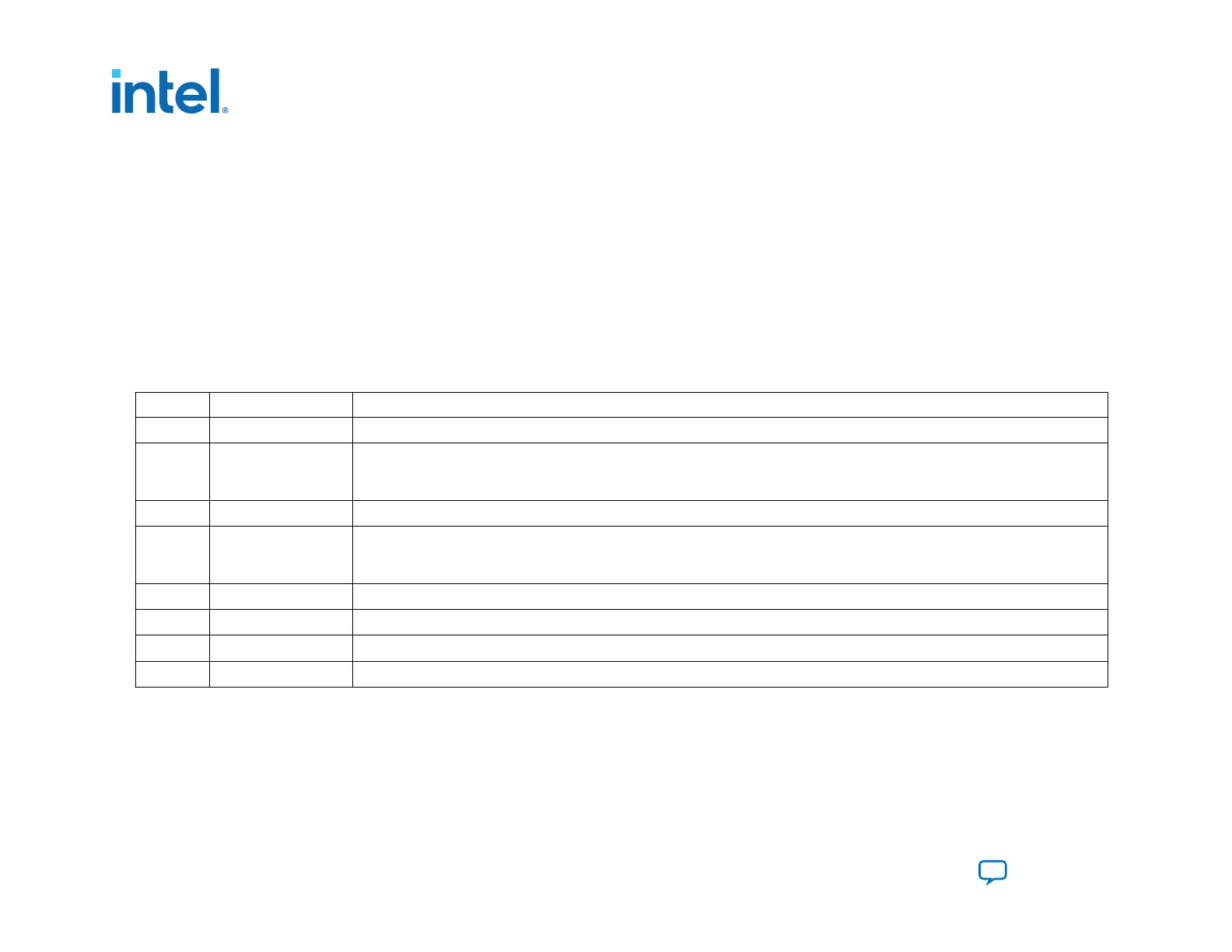

5.4.2.2. Sub-Partition Table Layout

The following table shows the structure of the sub-partition table. The Intel Quartus Prime Programming File Generator

software supports up to 126 partitions. Each sub-partition descriptor is 32 bytes.

Note: The firmware never updates the SPT.

Table 47. Sub-partition Table Layout

Offset Size (in bytes) Description

0x000

4 Magic number 0x57713427

0x004

4 Version number:

• 0 - before Intel Quartus Prime Pro Edition software version 20.4

• 1 - starting with Intel Quartus Prime Pro Edition software version 20.4

0x008

4 Number of entries

0x00C

4 Checksum:

• 0 - before Intel Quartus Prime Pro Edition software version 20.4

• CRC32 checksum - starting with Intel Quartus Prime Pro Edition software version 20.4

0x010

16 Reserved

0x020

32 Sub-partition Descriptor 1

0x040

32 Sub-partition Descriptor 2

0xFE0

32 Sub-partition Descriptor 126

Starting with Intel Quartus Prime Pro Edition software version 20.4, the SPT header contains a CRC32 checksum that is

computed over the whole SPT. The value of the CRC32 checksum filed itself is assumed as zero when the checksum is

computed. Refer to Application Image Layout on page 180 for the algorithm used to compute the CRC32 checksum. The

checksum is provided as a convenience so that SPT corruptions can better be detected by HPS software. By default the

feature is turned off.

5. Remote System Update (RSU)

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

176

Loading...

Loading...