5.4.2.3. Configuration Pointer Block Layout

The configuration pointer block contains a list of application image addresses. The SDM tries the images in sequence until one

of them is successful or all fail. The structure contains the following information:

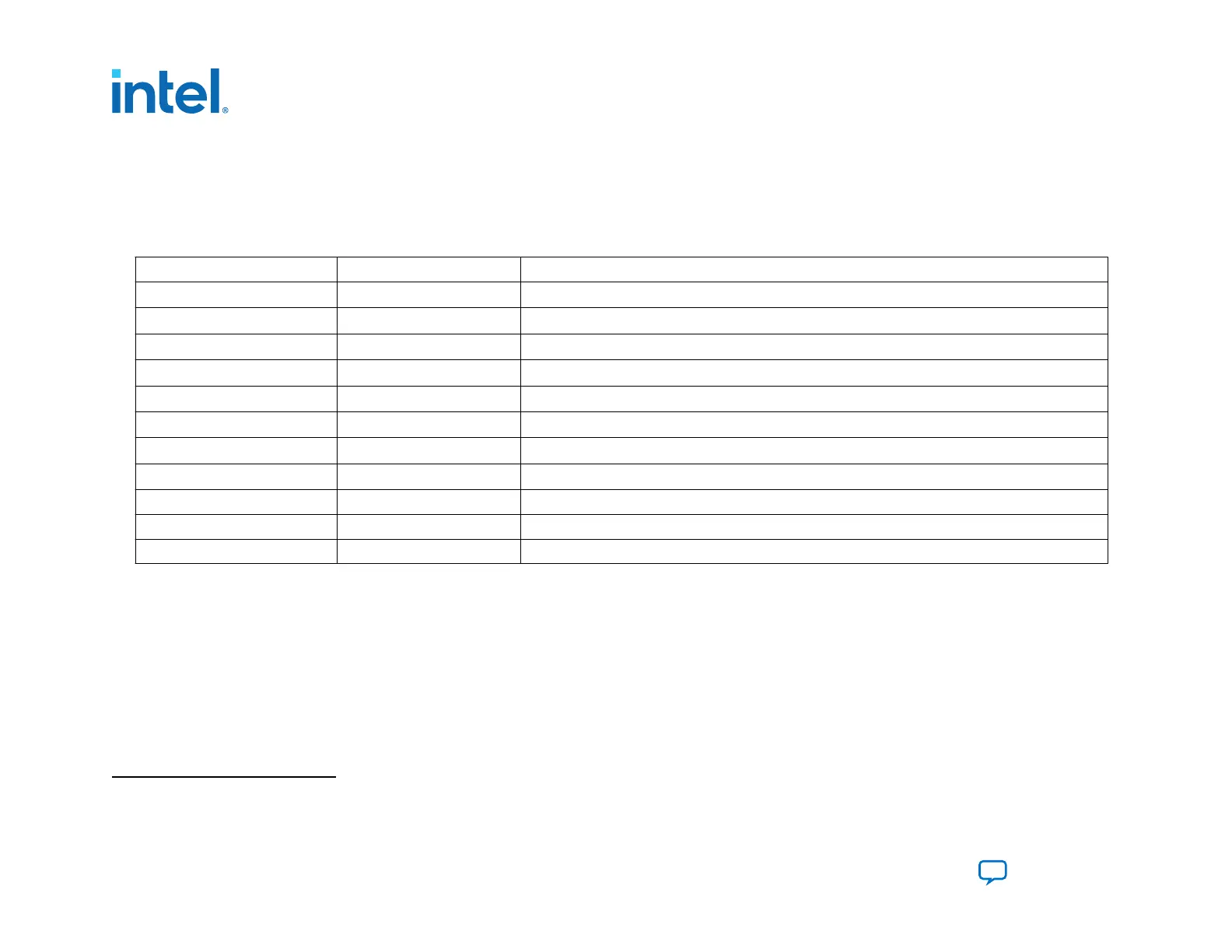

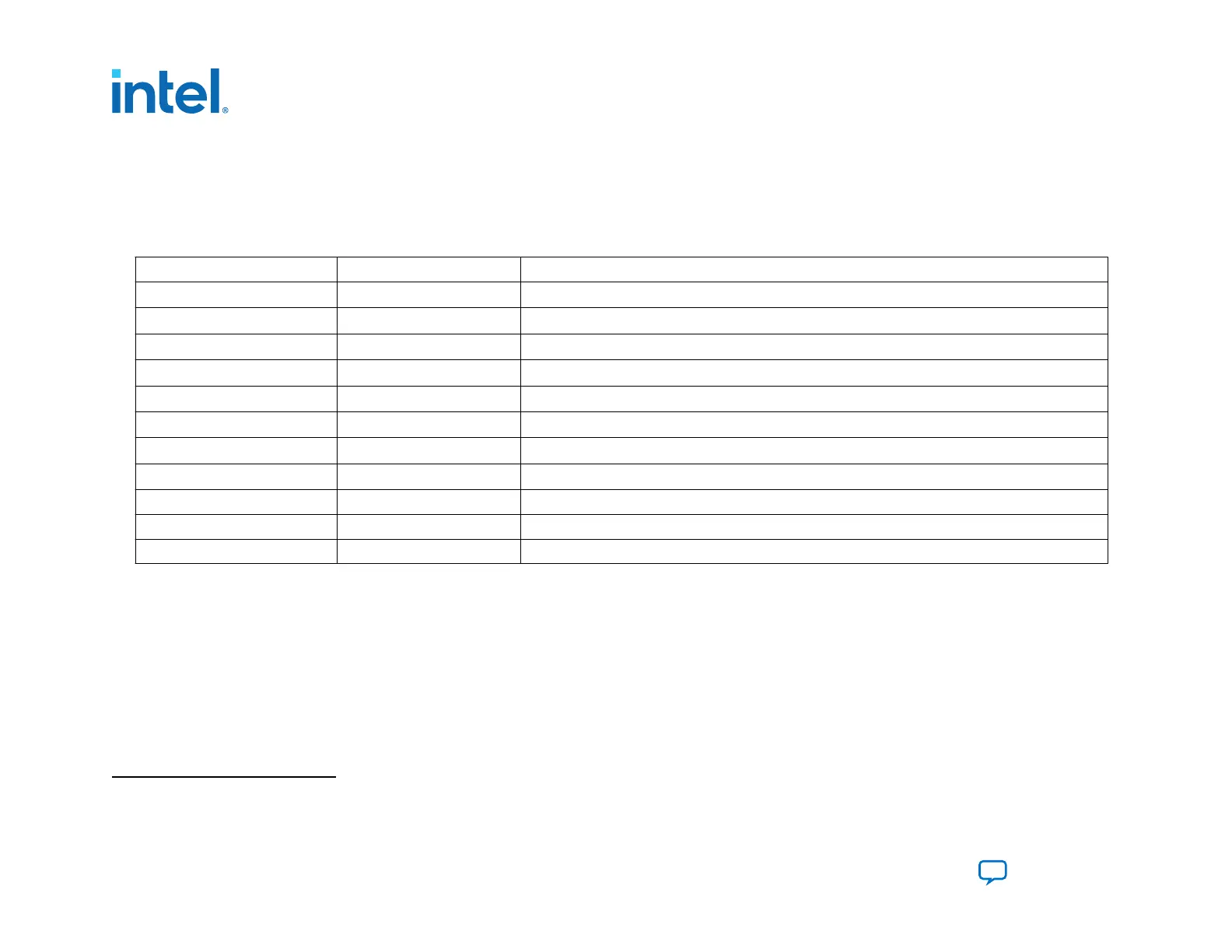

Table 50. Pointer Block Layout

Offset Size (in bytes) Description

0x00

4 Magic number 0x57789609

0x04

4 Size of pointer block header (0x18 for this document)

0x08

4 Size of pointer block (4096 for this document)

0x0C

4 Reserved

0x10

4 Offset to image pointers (IPTAB)

0x14

4

Number of image pointer slots (NSLOTS)

0x18

8 Reserved

0x20 (IPTAB)

(15)

8 First (lowest priority) image pointer slot (IPTAB)

8 Second (2nd lowest priority) image pointer slot

8 …

8 Last (highest priority) image pointer

The configuration pointer block can contain up to 508 application image pointers. The actual number is listed as NSLOTS. A

typical configuration pointer block update procedure consists of adding a new pointer and potentially clearing an older pointer.

Typically, the pointer block update uses one additional entry. Consequently, you can make 508 updates before the pointer

block must be erased. The erase procedure is called pointer block compression. This procedure is power failure safe, as there

are two copies of the pointer block. The copies are in different flash erase sectors. While one copy is being updated the other

copy is still valid.

Note: In order to successfully update CPBs, the HPS software (U-Boot or Linux) must be configured to have a QSPI erase granularity

of 32 KB or less. When configured with a coarser erase granularity (like 64 KB for example), the operation fails. All supported

flash devices offer erase granularities of 4 KB, 32 KB, and 64 KB, and the default for the current HPS software is 4 KB.

(15)

The offset may vary in future firmware updates.

5. Remote System Update (RSU)

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

178

Loading...

Loading...