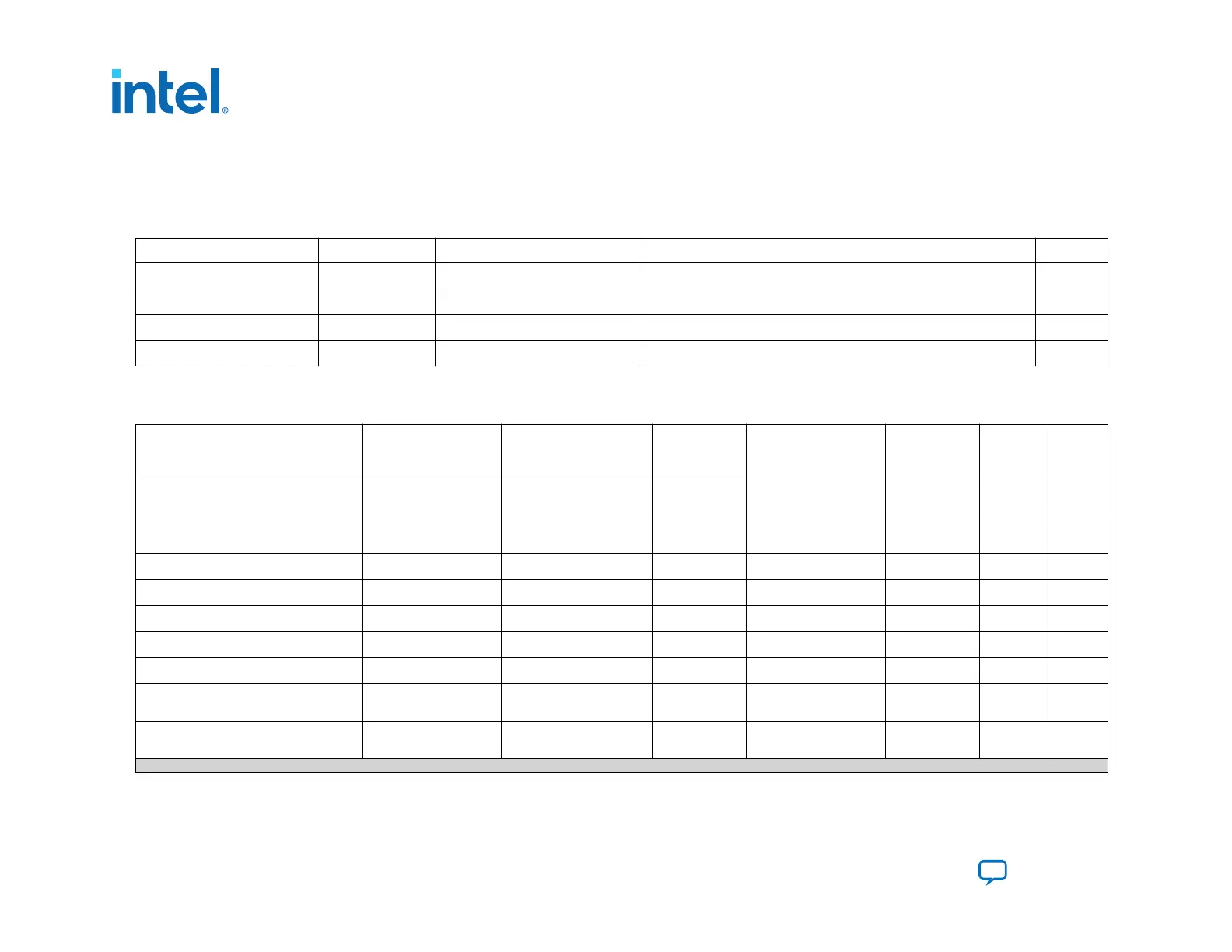

Table 11. Intel Agilex Avalon Streaming Interface ×16 or ×32 Configuration Scheme—Dedicated Configuration Pins

For all pin functions in this table:

• The I/O location is the SDM shared GPIO bank.

• The weak pull-up or pull-down, and open drain options are not applicable.

Pin Function Direction I/O Standard Drive Strength Slew Rate

AVST_CLK

Input 1.2 V LVCMOS — —

AVST_READY

Output 1.2 V LVCMOS Series 34 Ω OCT without calibration Slow

AVST_VALID

Input 1.2 V LVCMOS — —

AVST_DATA

Input 1.2 V LVCMOS — —

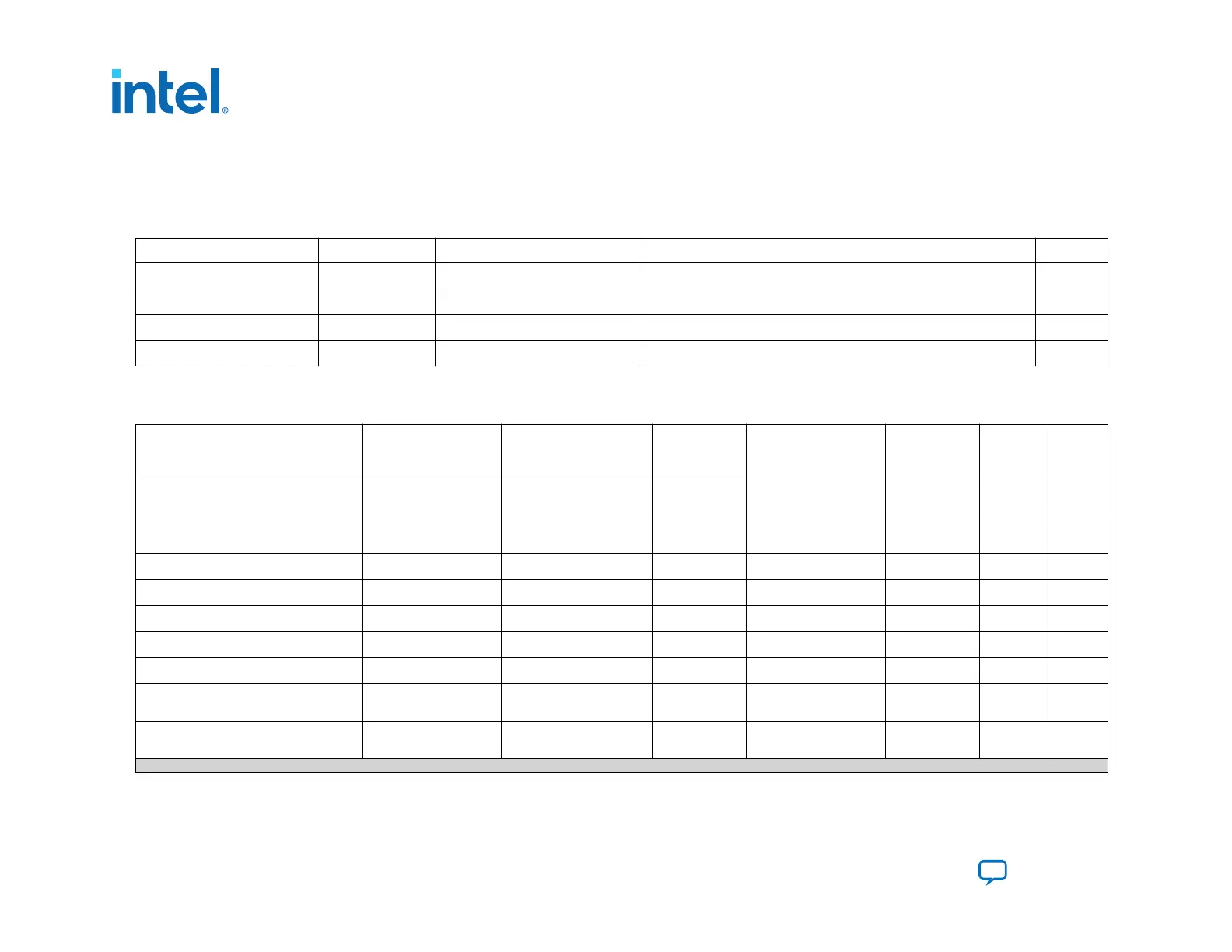

Table 12. Intel Agilex Optional Configuration Pins

The SDM I/O for each pin function in this table is as assigned in the Intel Quartus Prime configuration pins option.

Pin Function Direction I/O Standard Schmitt

Trigger/

TTL Input

Weak Pull-Up/

Pull-Down

Drive

Strength

Open

Drain

Slew

Rate

PWRMGT_SCL

Bidirectional 1.8V LVCMOS Schmitt

Trigger

Weak pull-up with

20 kΩ resistor

2 mA Enable Slow

PWRMGT_SDA

Bidirectional 1.8V LVCMOS Schmitt

Trigger

Weak pull-up with

20 kΩ resistor

2 mA Enable Slow

PWRMGT_ALERT

Output 1.8V LVCMOS — — 2 mA Enable Slow

CONF_DONE

Output 1.8V LVCMOS — — 8 mA Disable Fast

INIT_DONE

Output 1.8V LVCMOS — — 8 mA Disable Fast

CvP_CONFDONE

Output 1.8V LVCMOS — — 8 mA Disable Fast

SEU_ERROR

Output 1.8V LVCMOS — — 8 mA Disable Fast

HPS_COLD_nRESET

Bidirectional 1.8V LVCMOS Schmitt

Trigger

Weak pull-up with

20 kΩ resistor

2 mA Enable Fast

Direct to factory image

Input 1.8V LVCMOS Schmitt

Trigger

Weak pull-down with

20 kΩ resistor

— — —

continued...

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

44

Loading...

Loading...