A.7. Clock Circuitry

The development board includes a four channel programmable oscillator with a default

frequency of 25 MHz, 50 MHz, 100 MHz, and 125 MHz. The board also includes a 10

MHz programmable oscillator connected to the ADC.

A.7.1. On-Board Oscillators

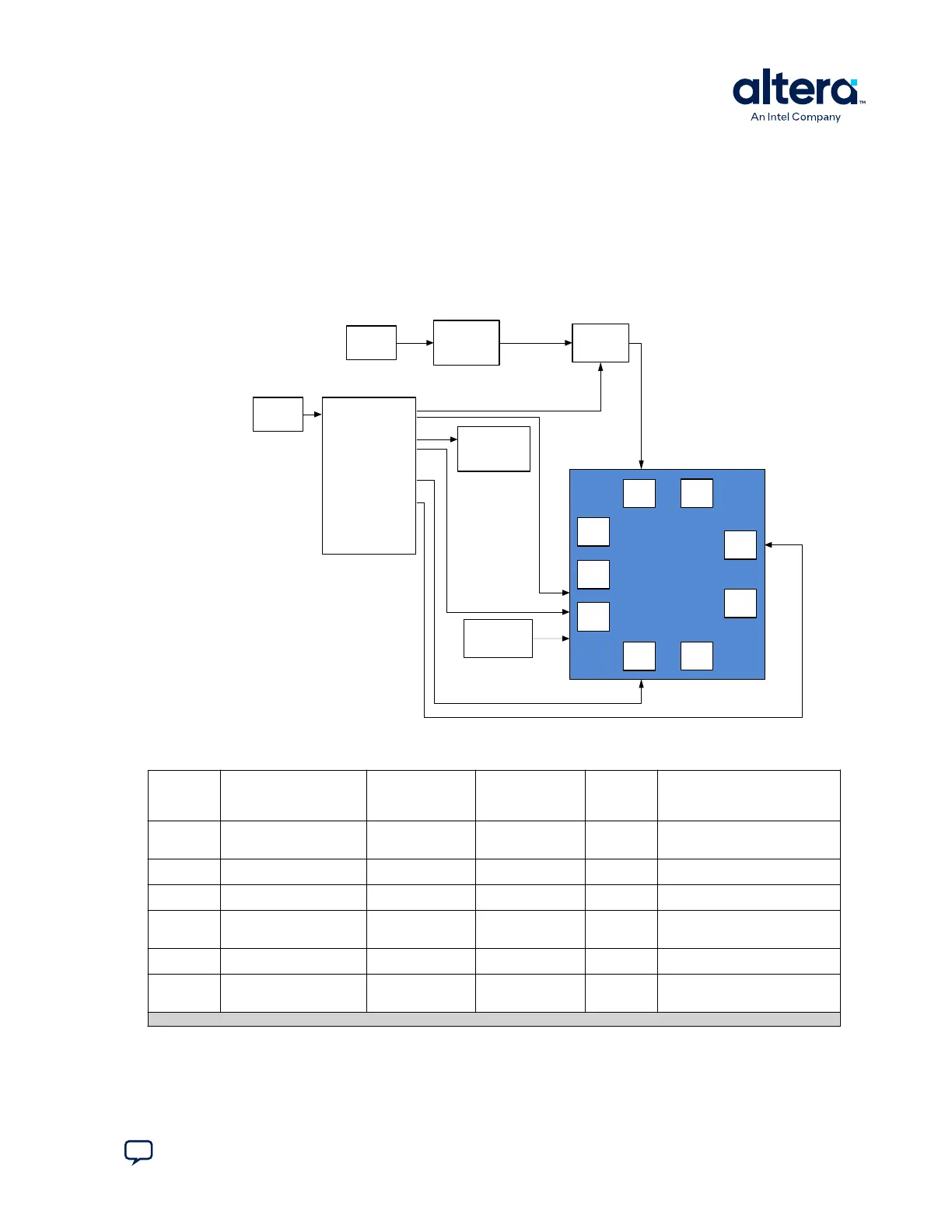

Figure 22. MAX 10 FPGA Development Board Clocks

IN

100M_DDR3

Bank 1A

Bank 1B

Bank 2

Bank 3

Bank 4

Bank 5

Bank 6

MAX® 10

Bank 7

Bank 8

USB_CLK

MAX® II

Intel® FPGA

Download Cable

USB_CLK

50M_MAXII

25M_ENET

50M_MAX10

25M_MAX10

125M_LVDS

ADC

Si5338

Default 50 MHz

Default 25 MHz

Default LVDS 125 MHz

Default LVDS 100 MHz

10/100/1000 Base-T

Ethernet PHY

88E1111 x2

Cypress

CY7C68013A

USB Controller

FA‐128

24 MHz XTAL

Si570

CMOS Clock Output

Default 10 MHz

8Y‐25MHz

XTAL

CH0

CH1

CH2

CH3

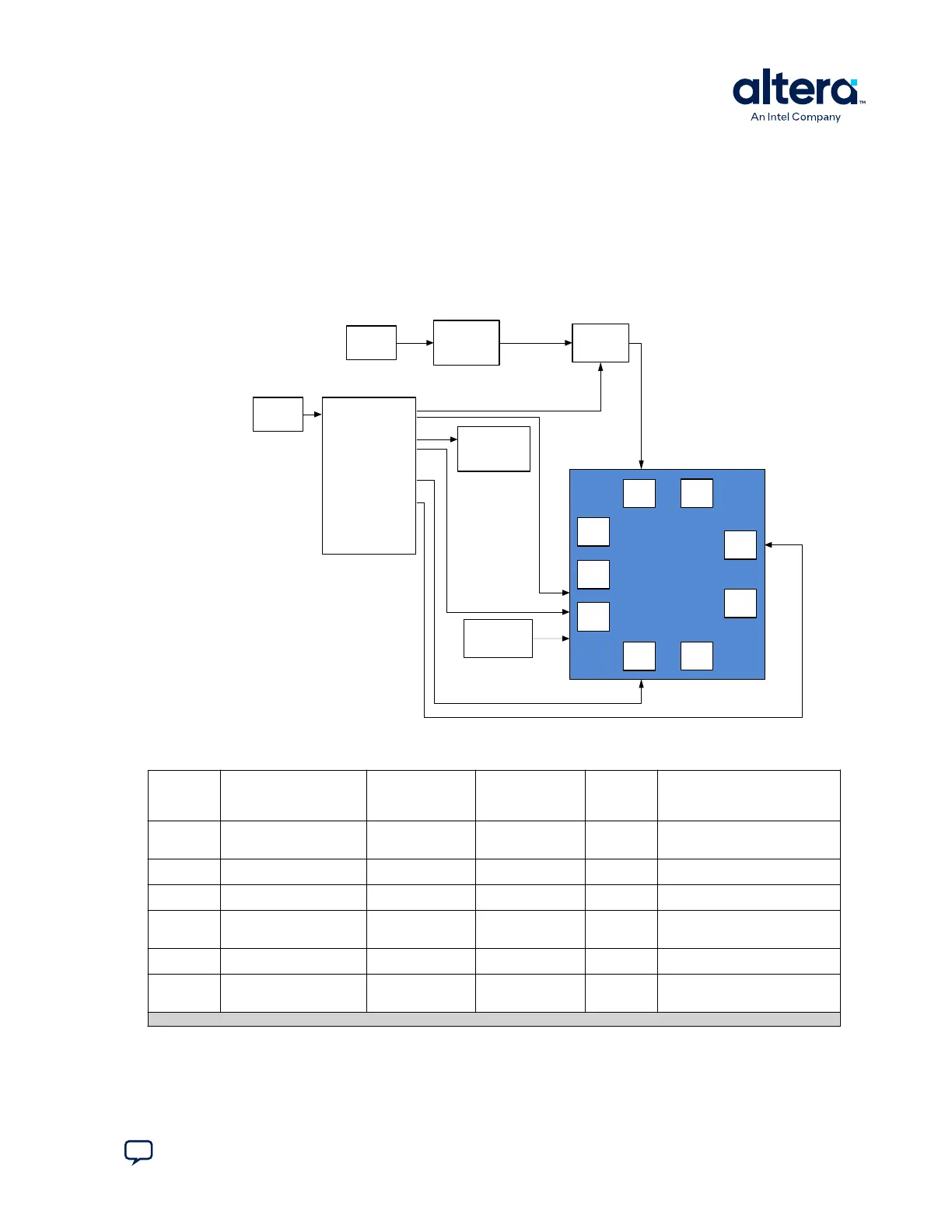

Table 24. On-Board Oscillators

Source Schematic Signal

Name

Frequency

(MHz)

I/O Standard MAX 10

FPGA Pin

Number

Application

X1

CLK_10_ADC

10.000 2.5 V CMOS N5 Programmable default 10 MHz

clock for ADC

U2

CLK_25_ENET

25.000 2.5 V CMOS — Ethernet clock

U2

CLK_25_MAX10

25.000 2.5 V CMOS M8 MAX 10 clock

U2

CLK_50_MAXII

25.000 2.5 V/3.3V CMOS — Clock for On-Board Intel FPGA

Download Cable II

U2

CLK_50_MAX10

50.000 2.5 V CMOS M9 MAX 10 clock

U2

CLK_DDR3_100_N

100.000 Differential

SSTL-15

N15 DDR3 clocks

continued...

A. Development Kit Components

683460 | 2024.11.20

Send Feedback

MAX

®

10 FPGA Development Kit User Guide

43

Loading...

Loading...