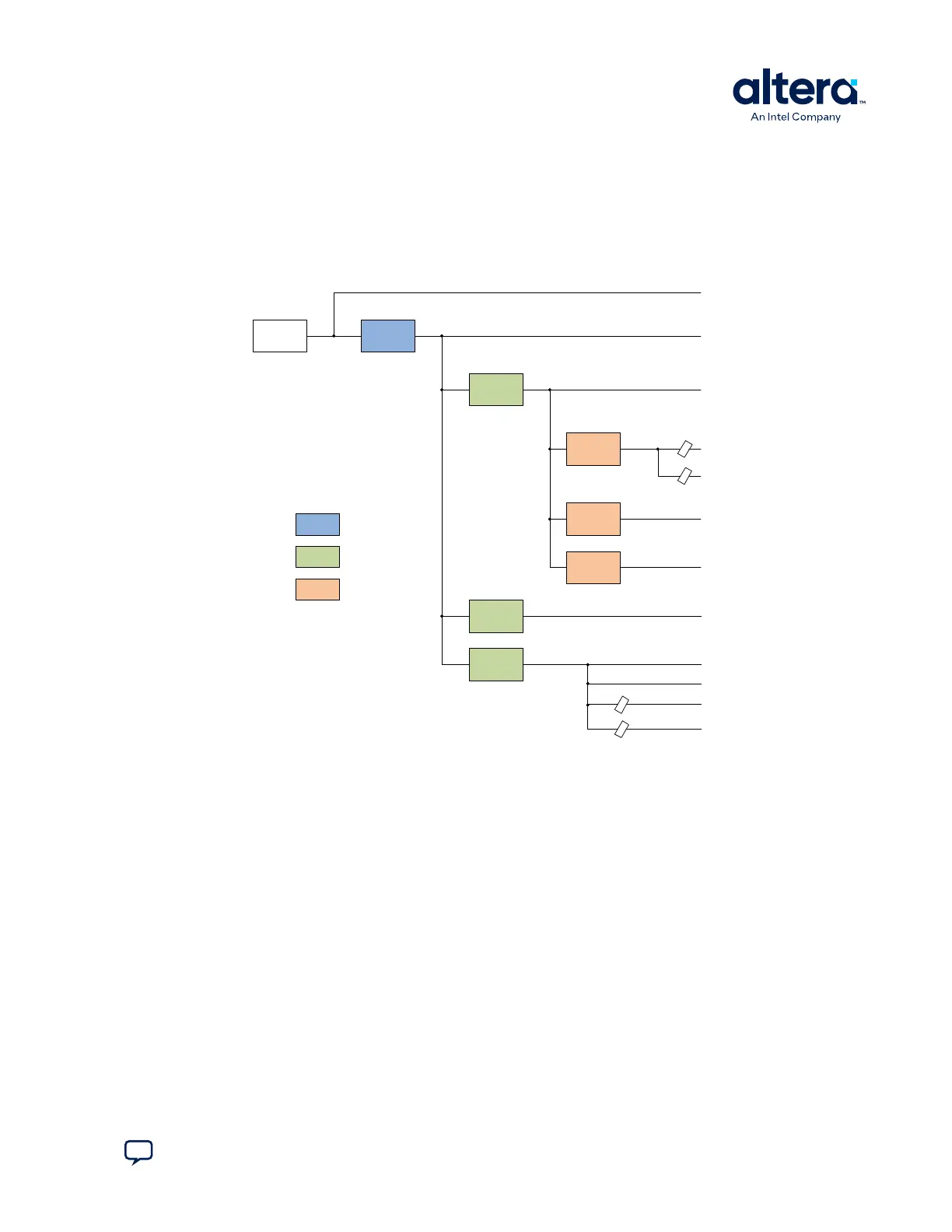

A.10. Power Distribution System

The following figure shows the power tree drawing for the MAX 10 FPGA development

board. Regulator inefficiencies and sharing are reflected in the currents shown, which

are conservative absolute maximum levels.

Figure 23. Power Distribution System

1

2

3

Power sequence

DC INPUT

12V 2A

EN 2342 QI

4A

12V @ 1000 mA

1.2V @ 1769 mA

2.5V_VCCA @ 55 mA

3.3V @ 2698 mA

5.0V @ 155 mA

2.5V_VCCADC

12V_HSMC @ 1000 mA

5V_HDMI @ 55 mA

5V_FT232 @ 100 mA

EN 6337 QI

3A

2.5V @ 55 mA

1.8V @ 53 mA

1.5V @ 426 mA

EN 6337 QI

3A

EN 6337 QI

3A

2.5V @ 1102 mA

2.5V_88E1111 @ 766 mA

2.5V_FT232R @ 15 mA

2.5V_VCCINT_MAXII @ 80 mA

2.5V_VCCIO_MAX10 @ 241 mA

1.2V_88E1111 @ 607 mA

1.2V_VCC @ 1128 mA

1.2V_VCCD @ 34 mA

1.2V_VCCADC

75 mm

75 mm

EP 5358 HUI

0.6A

EP 5358 HUI

0.6A

EP 5358 HUI

0.6A

14 mm

14 mm

14 mm

75 mm

200 mm

A. Development Kit Components

683460 | 2024.11.20

Send Feedback

MAX

®

10 FPGA Development Kit User Guide

61

Loading...

Loading...