A.8. Components and Interfaces

This section describes the development board's communication ports and interface

cards relative to the MAX 10 FPGA device.

A.8.1. 10/100/1000 Ethernet PHY

The MAX 10 FPGA Development Kit supports 10/100/1000 base-T Ethernet using an

external Marvell 88E1111 PHY and Triple-Speed Ethernet Intel FPGA IP MAC function.

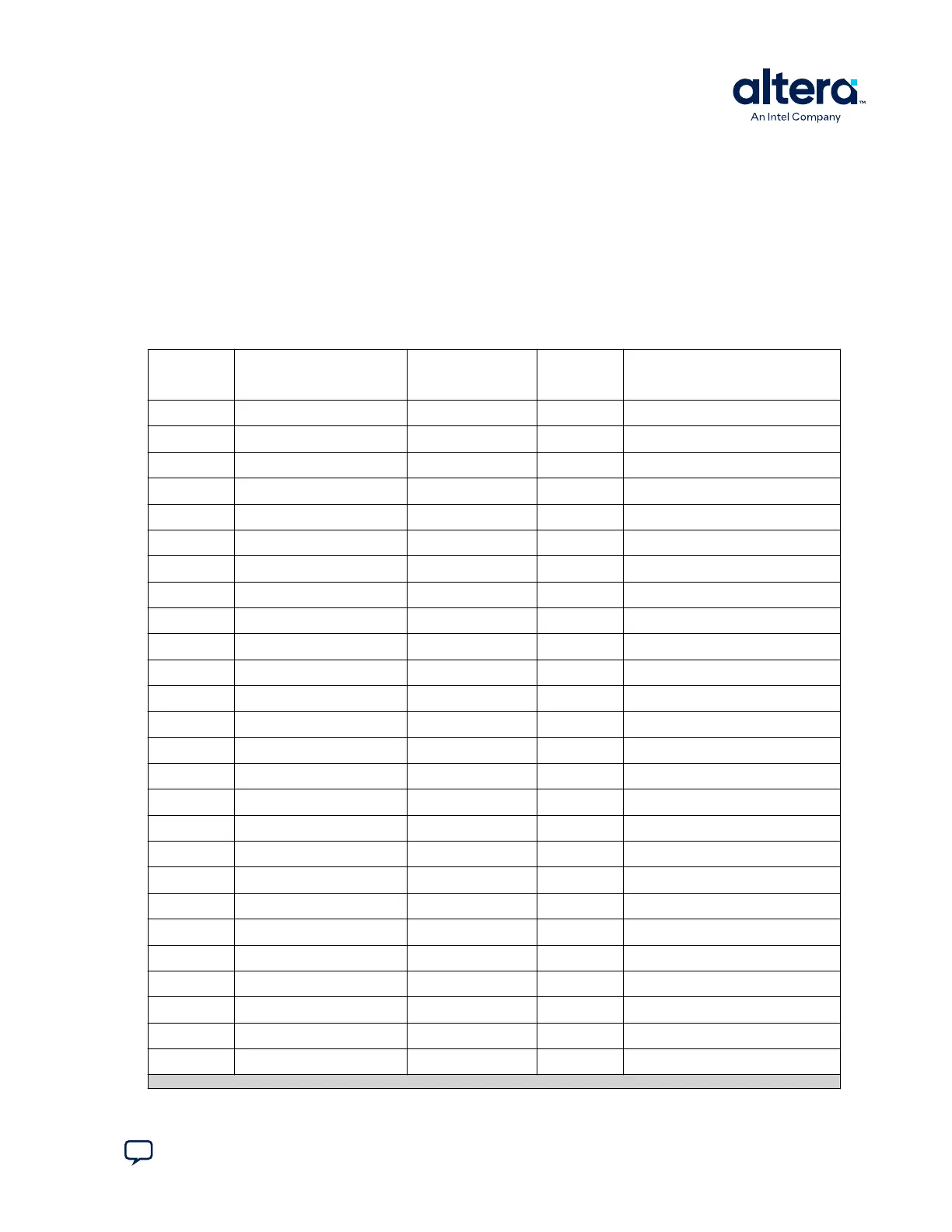

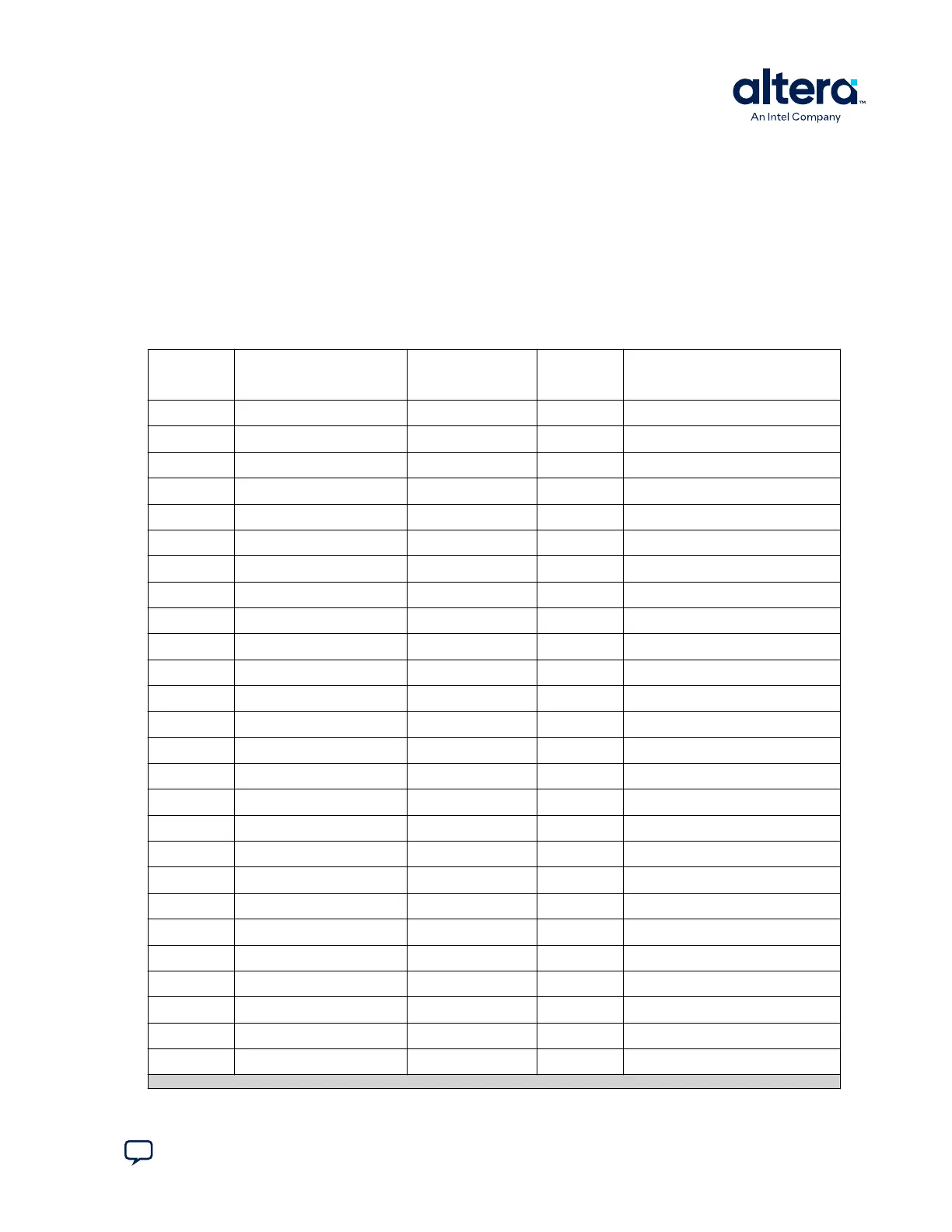

Table 27. Ethernet PHY A Pin Assignments, Signal Names, and Functions

Board

Reference

(U9)

Schematic Signal Name I/O Standard MAX 10

FPGA Pin

Number

Description

U9.8

ENETA_GTX_CLK

2.5V CMOS T5 125 MHz RGMII TX clock

U9.4

ENETA_TX_CLK

3.3V LVCMOS E10 25/2.5 MHz MII TX clock

U9.11

ENETA_TX_D0

2.5V CMOS R5 RGMII TX data 0

U9.12

ENETA_TX_D1

2.5V CMOS P5 RGMII TX data 1

U9.14

ENETA_TX_D2

2.5V CMOS W1 RGMII TX data 2

U9.16

ENETA_TX_D3

2.5V CMOS W2 RGMII TX data 3

U9.9

ENETA_TX_EN

2.5V CMOS R4 RGMII TX enable

U9.7

ENETA_TX_ER

2.5V CMOS P4 MII TX error

U9.2

ENETA_RX_CLK

2.5V CMOS P3 RGMII RX clock

U9.95

ENETA_RX_D0

2.5V CMOS N9 RGMII RX data 0

U9.92

ENETA_RX_D1

2.5V CMOS T1 RGMII RX data 1

U9.93

ENETA_RX_D2

2.5V CMOS N1 RGMII RX data 2

U9.91

ENETA_RX_D3

2.5V CMOS T3 RGMII RX data 3

U9.94

ENETA_RX_DV

2.5V CMOS T2 RGMII RX valid

U9.3

ENETA_RX_ER

2.5V CMOS U2 MII RX error

U9.28

ENETA_RESETN

2.5V CMOS V8 Device reset

U9.23

ENETA_INTn

2.5V CMOS V7 Management bus interrupt

U9.25

ENET_MDC

2.5V CMOS Y6 MDI clock

U9.24

ENET_MDIO

2.5V CMOS Y5 MDI data

U9.84

ENETA_RX_CRS

2.5V CMOS N8 MII Carrier Sense

U9.83

ENETA_RX_COL

2.5V CMOS P1 MII Collision

U9.55

CLK_25_ENET

2.5V CMOS — 25 MHz Reference clock

U9.70

ENETA_LED_DUPLEX

2.5 V CMOS — Duplex or collision LED

U9.76

ENETA_LED_LINK10

2.5 V CMOS — 10 Mb link LED

U9.74

ENETA_LED_LINK100

2.5V CMOS R9 100 Mb link LED

U9.73

ENETA_LED_LINK1000

2.5V CMOS — 1000 Mb link LED

continued...

A. Development Kit Components

683460 | 2024.11.20

Send Feedback

MAX

®

10 FPGA Development Kit User Guide

45

Loading...

Loading...