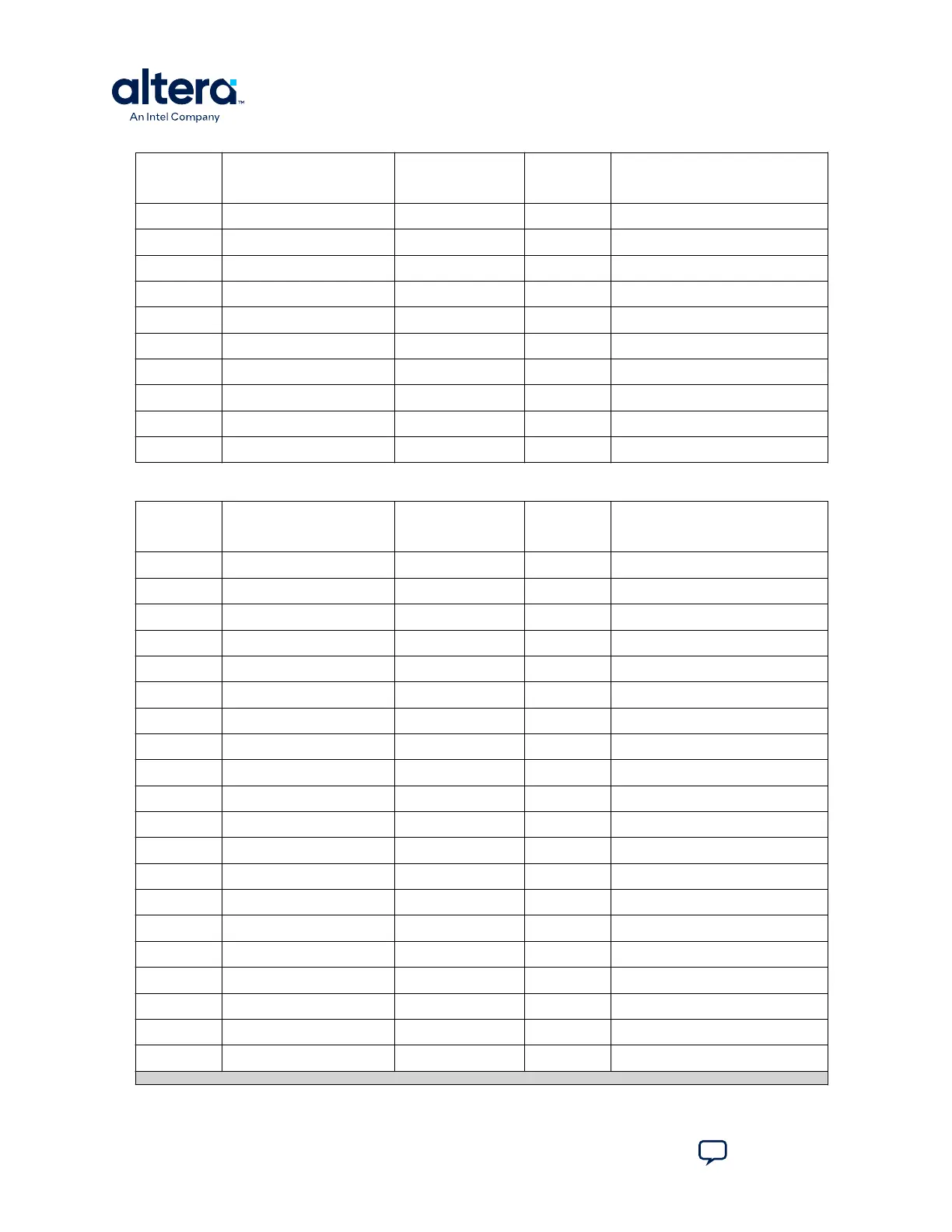

Board

Reference

(U9)

Schematic Signal Name I/O Standard MAX 10

FPGA Pin

Number

Description

U9.58, 69

ENETA_LED_RX

2.5V CMOS — RX data active LED

U9.61, 68

ENETA_LED_TX

2.5V CMOS — TX data active LED

U9.29

ENETA_MDI_P0

2.5V CMOS — MDI

U9.31

ENETA_MDI_N0

2.5V CMOS — MDI

U9.33

ENETA_MDI_P1

2.5V CMOS — MDI

U9.34

ENETA_MDI_N1

2.5V CMOS — MDI

U9.39

ENETA_MDI_P2

2.5V CMOS — MDI

U9.41

ENETA_MDI_N2

2.5V CMOS — MDI

U9.42

ENETA_MDI_P3

2.5V CMOS — MDI

U9.43

ENETA_MDI_N3

2.5V CMOS — MDI

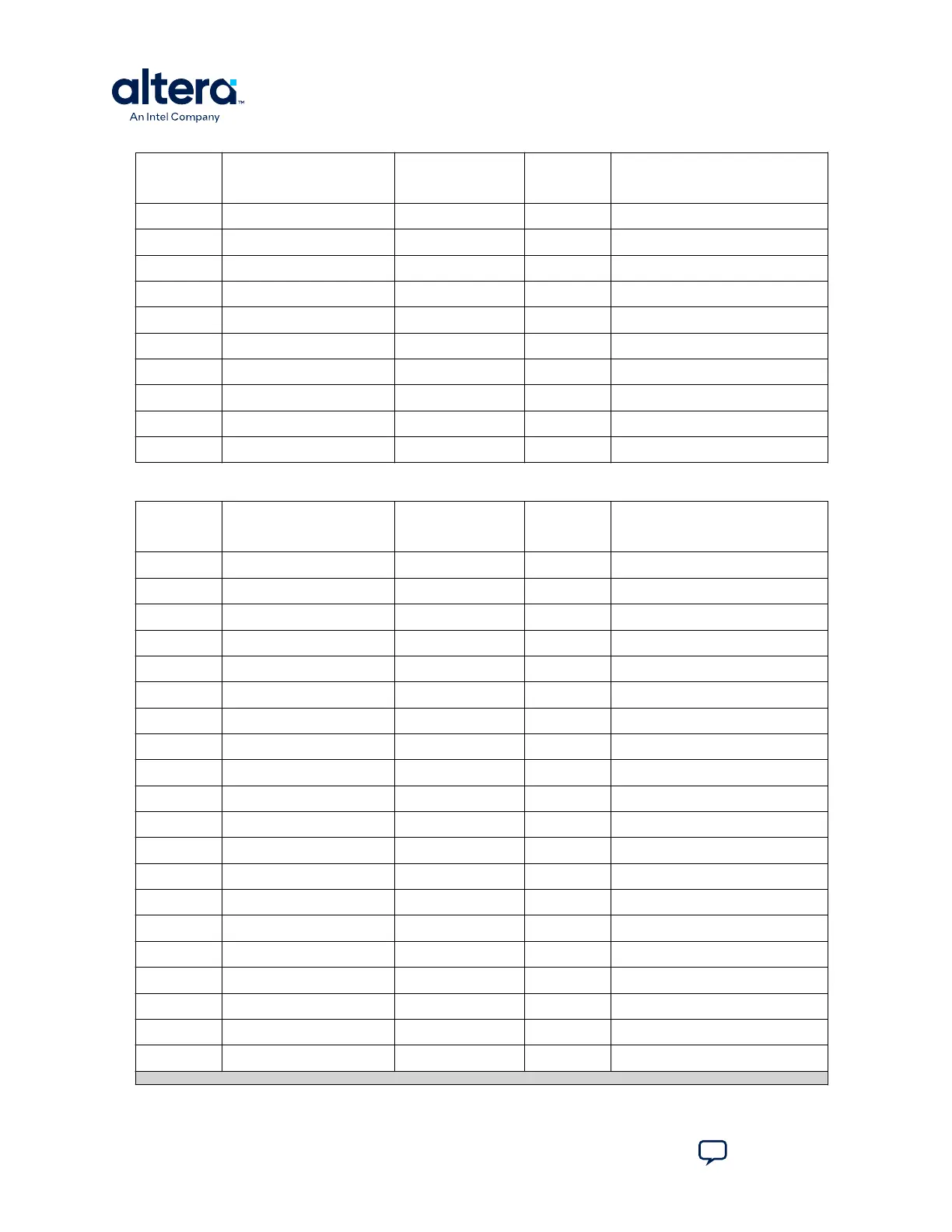

Table 28. Ethernet PHY B Pin Assignments, Signal Names and Functions

Board

Reference

(U10)

Schematic Signal Name I/O Standard Max 10

FPGA Pin

Number

Description

U10.8

ENETB_GTX_CLK

2.5V CMOS T6 125 MHz RGMII TX clock

U10.4

ENETB_TX_CLK

3.3V LVCMOS E11 25/2.5 MHz MII TX clock

U10.11

ENETB_TX_D0

2.5V CMOS U1 RGMII TX data 0

U10.12

ENETB_TX_D1

2.5V CMOS V1 RGMII TX data 1

U10.14

ENETB_TX_D2

2.5V CMOS U3 RGMII TX data 2

U10.16

ENETB_TX_D3

2.5V CMOS U4 RGMII TX data 3

U10.9

ENETB_TX_EN

2.5V CMOS V3 RGMII TX enable

U10.7

ENETB_TX_ER

2.5V CMOS U5 MII TX error

U10.2

ENETB_RX_CLK

2.5V CMOS R3 RGMII RX clock

U10.95

ENETB_RX_D0

2.5V CMOS P8 RGMII RX data 0

U10.92

ENETB_RX_D1

2.5V CMOS M1 RGMII RX data 1

U10.93

ENETB_RX_D2

2.5V CMOS M2 RGMII RX data 2

U10.91

ENETB_RX_D3

2.5V CMOS R7 RGMII RX data 3

U10.94

ENETB_RX_DV

2.5V CMOS R1 RGMII RX valid

U10.3

ENETB_RX_ER

2.5V CMOS R2 MII RX error

U10.28

ENETB_RESETn

2.5V CMOS AB4 Device reset

U10.23

ENETB_INTn

2.5V CMOS AA3 Management bus interrupt

U10.25

ENET_MDC

2.5V CMOS Y6 MDI clock

U10.24

ENET_MDIO

2.5V CMOS Y5 MDI data

U10.84

ENETB_RX_CRS

2.5V CMOS N3 MII Carrier Sense

continued...

A. Development Kit Components

683460 | 2024.11.20

MAX

®

10 FPGA Development Kit User Guide

Send Feedback

46

Loading...

Loading...