Intel® Server Board S5500WB TPS Functional Architecture

Revision 1.3

Intel order number E53971-004

27

• Manageability Engine (ME) subsystem

3.5.1 IOH24D PCI Express*

PCI Express* Gen1 and Gen2 are dual-simplex, point-to point serial differential low-voltage

interconnects. The signaling bit rate is 2.5 Gb/s one direction per lane for Gen1 and 5.0 Gb/s

one direction per lane for Gen2. Each port consists of a transmitter and receiver pair. A link

between the ports of two devices is a collection of lanes (x1, x2, x4, x8, x16, and so forth). All

lanes within a port must transmit data using the same frequency. The following table lists the

usage of the IOH24D PCI Express* bus segments.

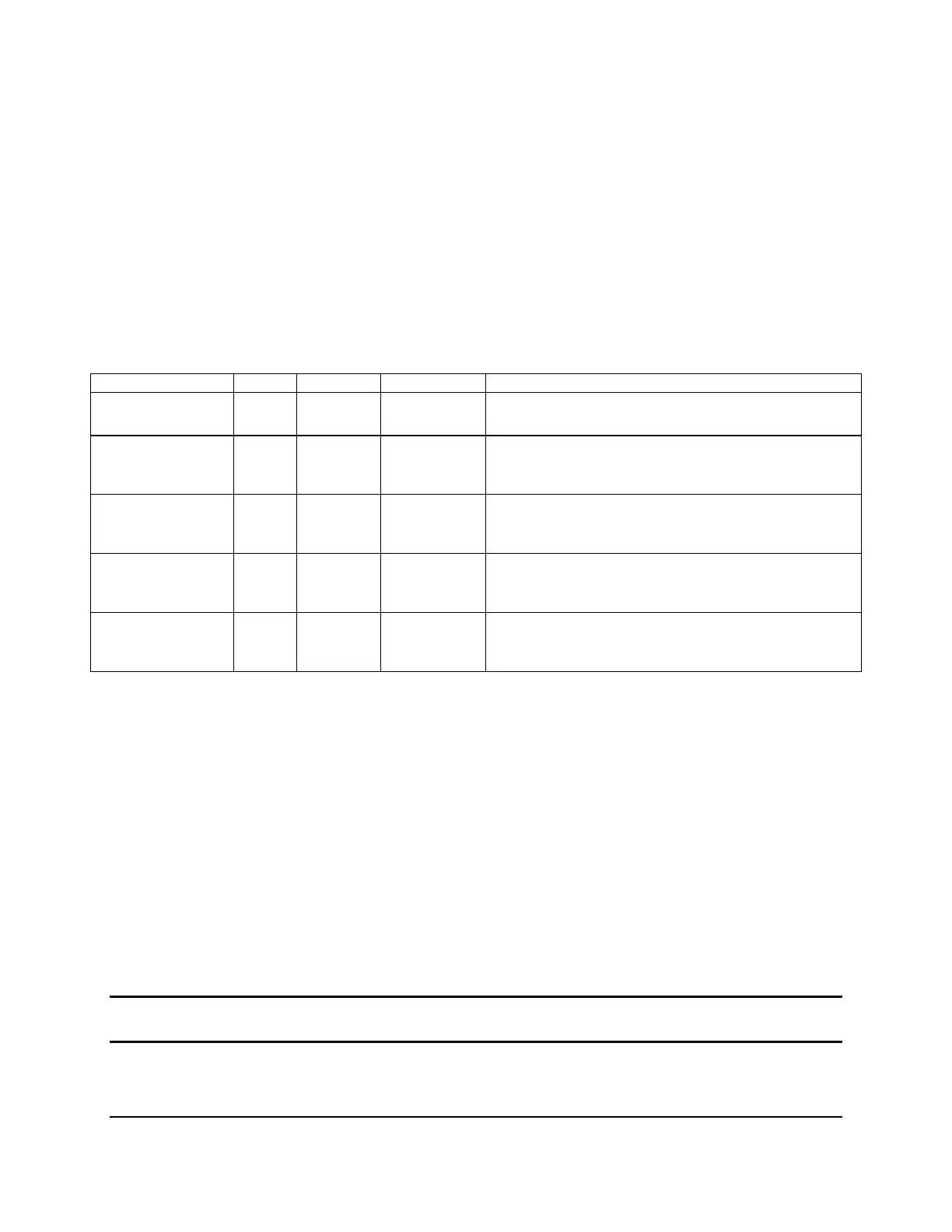

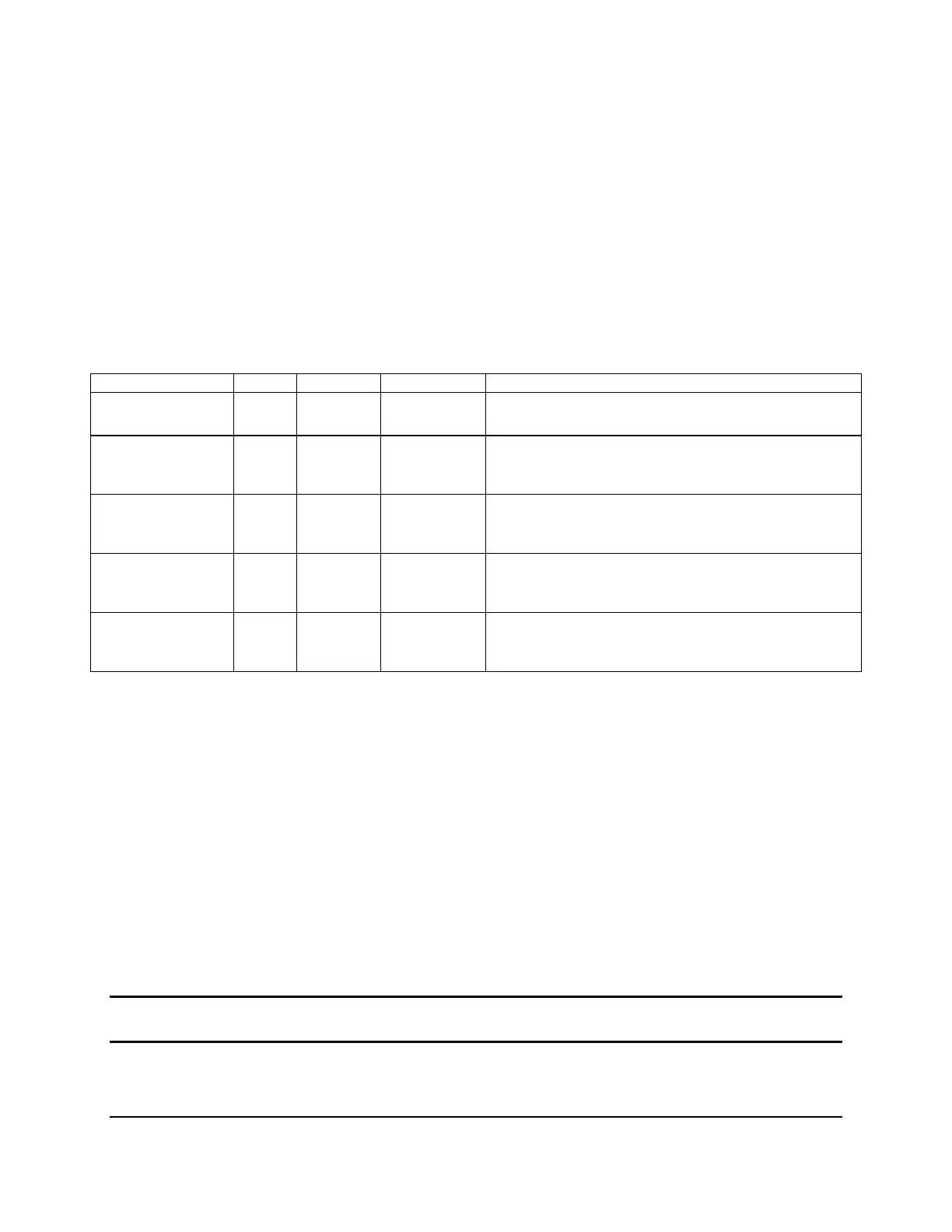

Table 6. IOH24D PCI Express* Bus Segments

PCI Bus Segment Width Speed Type PCI I/O Card Slots

Port 0

ICH10R

x4 10 Gb/s PCI Express*

Gen1

x4 PCI Express* Gen1 throughput to the ICH10R

southbridge

PE1, PE2

Intel

®

5500 Chipset

IOH PCI Express*

x4 10 Gb/s PCI Express*

Gen1

x4 PCI Express* Gen1 throughput to an onboard NIC.

PE3,

Intel

®

5500 Chipset

IOH PCI Express*

X4 20 Gb/S PCI Express*

Gen2

X4 PCI Express* Gen2 throughput to slot 1.

PE7, PE8

Intel

®

5500 Chipset

IOH PCI Express*

x8 40 Gb/S PCI Express*

Gen2

x8 PCI Express* Gen2 throughput to the slot 6 riser .

PE9, PE10

Intel

®

5500 Chipset

IOH PCI Express*

x8 40 Gb/S PCI Express*

Gen2

x4 PCI Express* Gen2 throughput to each of the two Intel

®

I/O Expansion Module connectors.

3.5.1.1 Direct Cache Access (DCA)

The DCA mechanism is a system-level protocol in a multi-processor system to improve I/O

network performance by providing higher system performance. It is designed to minimize cache

misses when a demand read is executed. This is accomplished by placing the data from the I/O

devices directly into the CPU cache through hints to the processor to perform a data pre-fetch

and install it in its local caches. The Intel

®

5500 series processor supports Direct Cache Access

(DCA). You enable or disable DCA in the BIOS processor setup menu.

3.5.1.2 Intel

®

Virtualization Technology for Directed I/O (Intel

®

VT-d)

The Intel

®

Virtualization Technology is designed to support multiple software environments

sharing the same hardware resources. Each software environment may consist of an operating

system and applications. You can enable or disable the Intel

®

Virtualization Technology in the

BIOS setup. The default behavior is disabled.

Note: If the setup options are changed to enable or disable the Virtualization Technology setting

in the processor, the user must perform an AC power cycle for the changes to take effect.

Loading...

Loading...