04/01/2015 Inventec Corp. Confidential 76

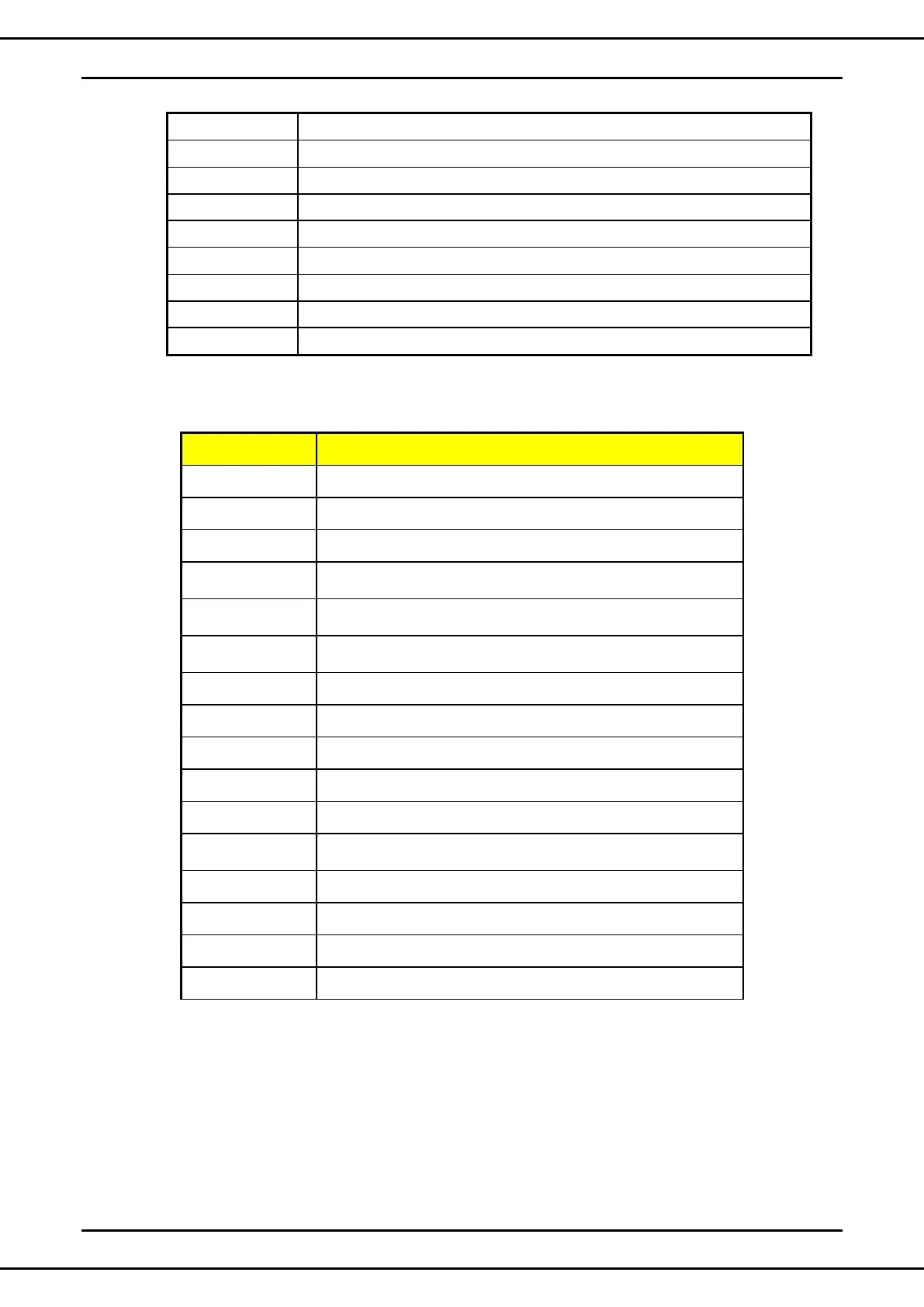

Unspecified memory initialization error.

Invalid CPU type or Speed

CPU self test failed or possible CPU cache error

CPU micro-code is not found or micro-code update is failed

reset PPI is not available

Reserved for future AMI error codes

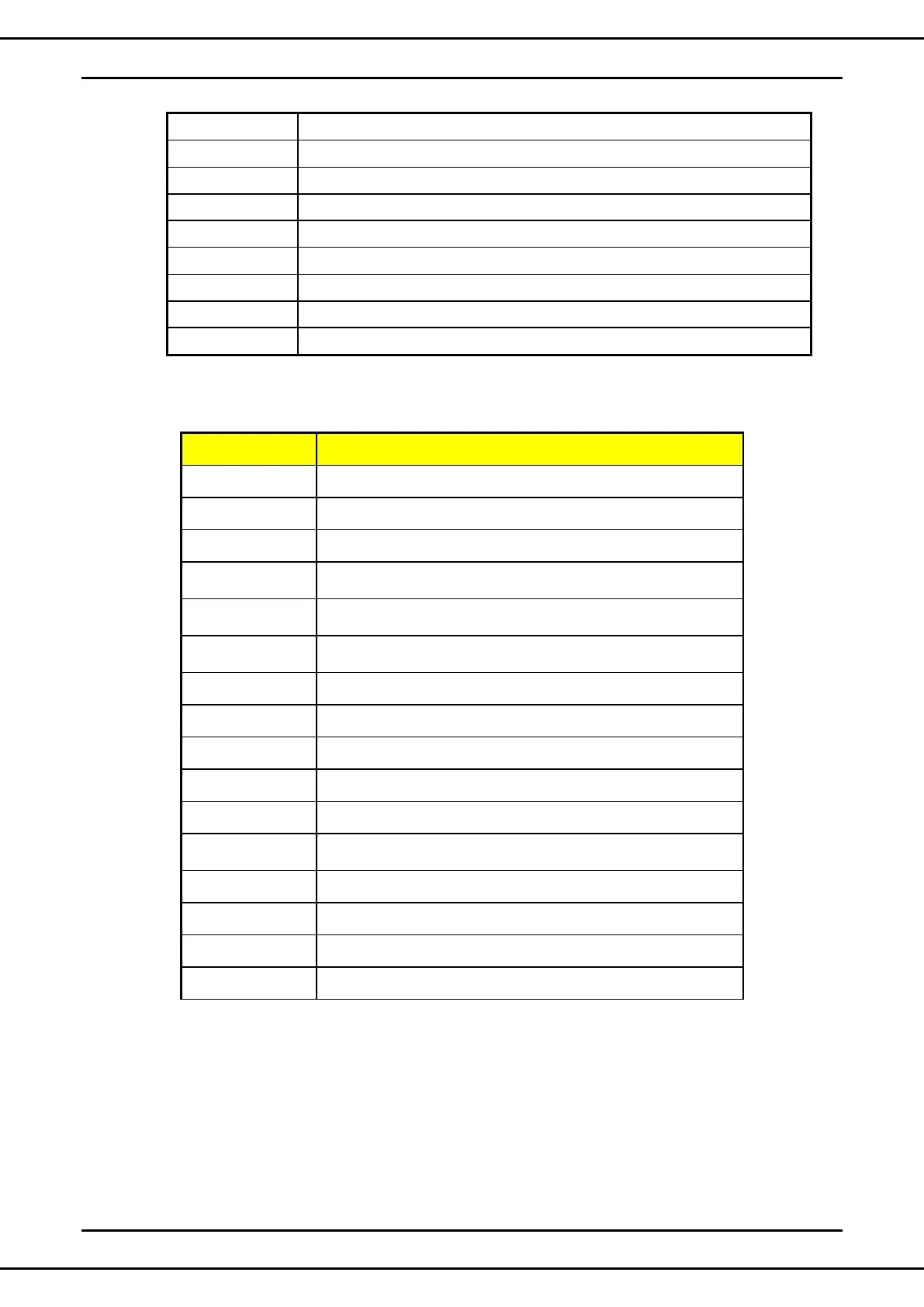

4.2.5. Memory Reference Code Checkpoints

STS_DIMM_DETECT: Detect DIMM population

STS_CLOCK_INIT: Set DDR frequency

STS_SPD_DATA: Gather remaining SPD data

STS_GLOBAL_EARLY: Program registers on the memory

controller level

STS_RANK_DETECT: Evaluate RAS modes and save rank

information

STS_CHANNEL_EARLY: Program registers on the channel

level

STS_DDRIO_INIT: DDRIO Initialization sequence

STS_DDR_CHANNEL_TRAINING: Train DDR

STS_INIT_THROTTLING: Initialize CLTT/OLTT

STS_MEMBIST: Hardware memory test and init

STS_MEMINIT: Execute memory init

STS_DDR_MEMMAP: Program memory map and

interleaving

STS_RAS_CONFIG: Program RAS configuration

STS_MRC_DONE: MRC is done

Loading...

Loading...