Modbus I/O Access

270 IOLAN SDS/SCS/STS User’s Guide, Version 3.6

Serial Port Coil/Register Descriptions

This section contains descriptions of serial port coils:

z MB_REG_DI_DSR—The status of the DSR input signal. 1 is Active, 0 is Inactive. If Invert

Signal

is configured on, 0 is Active, 1 is Inactive. If input is Latched, returns latched status.

z MB_REG_DI_DSR_ALARM_STATE—The alarm state of DSR input signal. 1 is In Alarm

state, 0 is Not in Alarm state. A write of any value clears the alarm state.

z MB_REG_DI_DCD—The status of DCD line. 1 is Active, 0 is Inactive. If Invert Signal is

configured

on, 0 is Active, 1 is Inactive.

z MB_REG_DI_DCD_ALARM_STATE—The alarm state of DCD input signal. 1 is in Alarm

state, 0 is Not in Alarm state. A write of any value clears the alarm state.

z MB_REG_DI_CTS—The status of CTS input signal. 1 is Active, 0 is Inactive. If Invert Signal

is configured

on, 0 is Active, 1 is Inactive.

z MB_REG_DI_CTS_ALARM_STATE—The alarm state of CTS input signal. 1 is Alarm, 0 is

Not in Alarm. A write of any value clears the alarm state.

z MB_REG_DO_DTR—The status of DTR output signal. 1 is Active, 0 is Inactive.

z MB_REG_DO_RTS—The status of RTS output signal. 1 is Active, 0 is Inactive.

This section contains descriptions of serial port holding registers:

z MB_REG_HR_DI_DSR_LATCH—The latched status for the DSR signal. 1 is Latched, 0 is

Not Latched. A write any value will clear the latch.

z MB_REG_HR_DI_DCD_LATCH—The latched status for the DCD signal. 1 is Latched, 0 is

Not Latched. A write any value will clear the latch.

z MB_REG_HR_DI_CTS_LATCH—The latched status for the CTS signal. 1 is Latched, 0 is

Not Latched. A write any value will clear the latch.

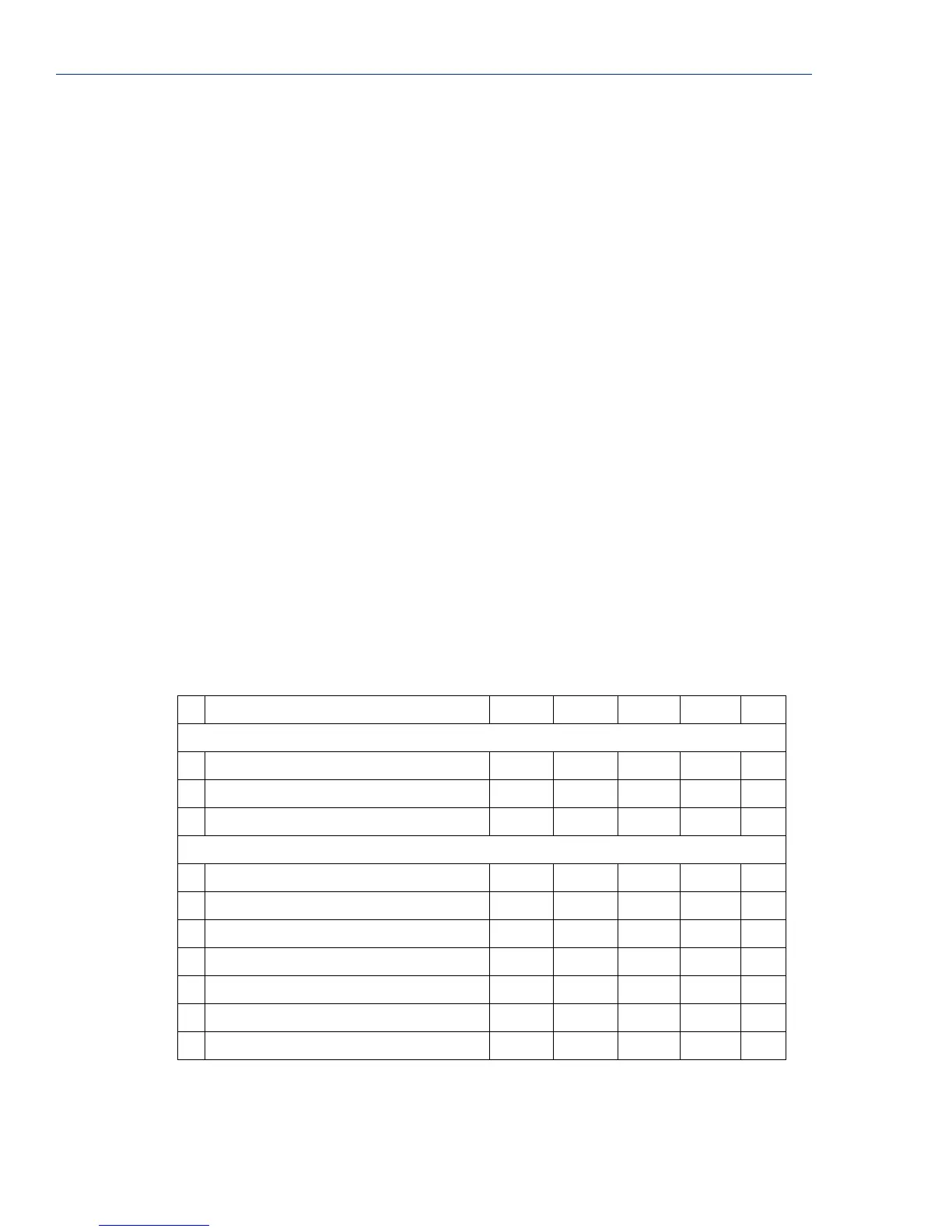

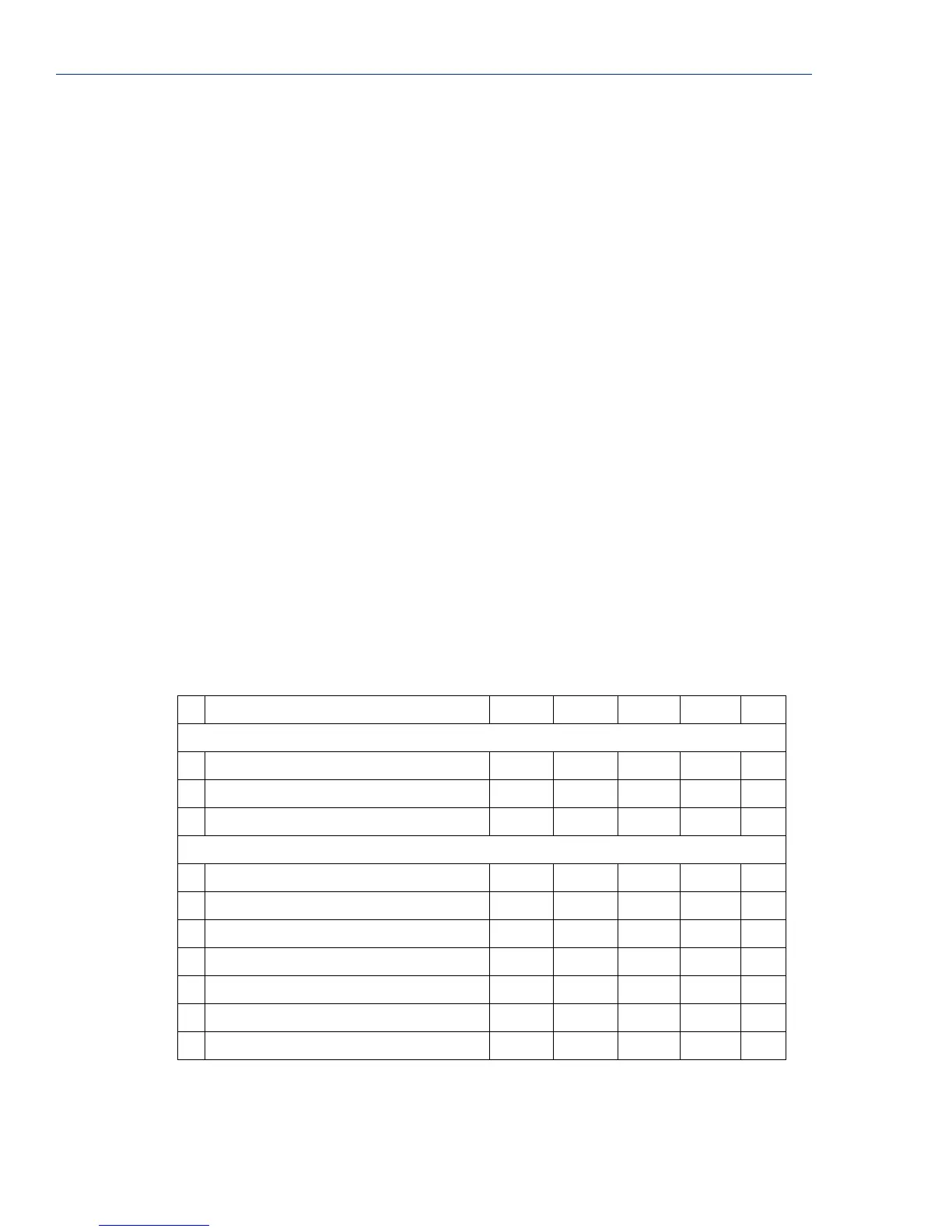

A4/T4 Registers

The following registers are supported by the IOLAN A4 and T4 Input models:

Data Model A1/T1 A2/T2 A3/T3 A4/T4 R/W

Holding Registers:

MB_REG_HR_AI_CLEAR_ALARM_LATCH 2049 2050 2051 2052 W

MB_REG_HR_AI_CLEAR_MAX 2113 2114 2115 2116 W

MB_REG_HR_AI_CLEAR_MIN 2177 2178 2179 2180 W

Input Registers:

MB_REG_IR_CURR_ENG 2080 2112 2144 2176 R

MB_REG_IR_MIN_ENG 2082 2114 2146 2178 R

MB_REG_IR_MAX_ENG 2084 2116 2148 2180 R

MB_REG_IR_CURR_RAW 2086 2118 2150 2182 R

MB_REG_IR_MIN_RAW 2087 2119 2151 2183 R

MB_REG_IR_MAX_RAW 2088 2120 2152 2184 R

MB_REG_IR_ALARM_LEVEL 2089 2121 2153 2185 R

Loading...

Loading...