RL78/G13 CHAPTER 29 ELECTRICAL SPECIFICATIONS

R01UH0146EJ0100 Rev.1.00 1030

Sep 22, 2011

Caution The pins mounted depend on the product. Refer to 2.1.1 20-pin products to 2.1.14 128-pin products,

and 2.1.15 Pins for each product (pins other than port pins).

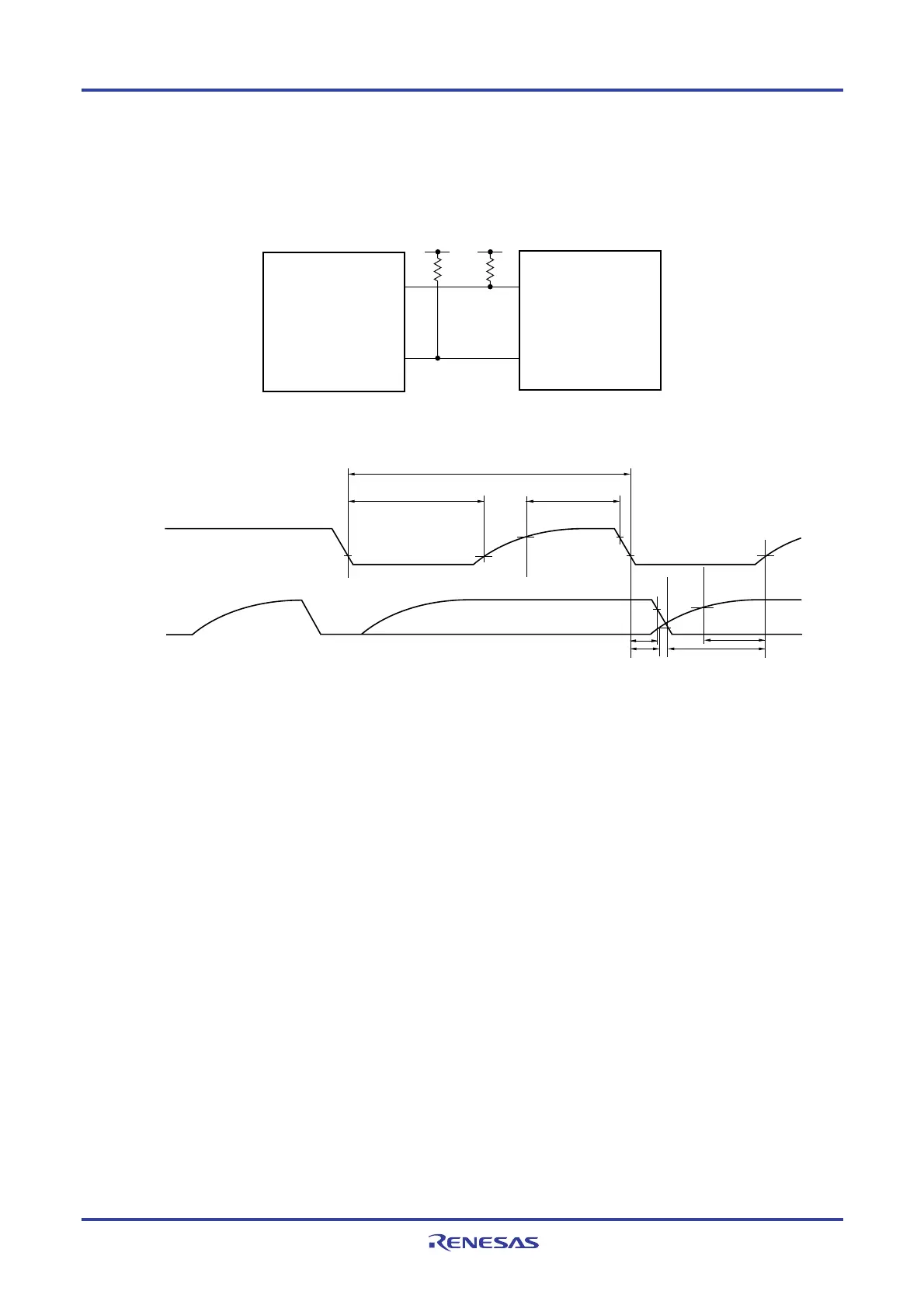

Simplified I

2

C mode connection diagram (during communication at different potential)

User's device

SDAr

SCLr

SDA

SCL

V

b

R

b

V

b

R

b

RL78/G13

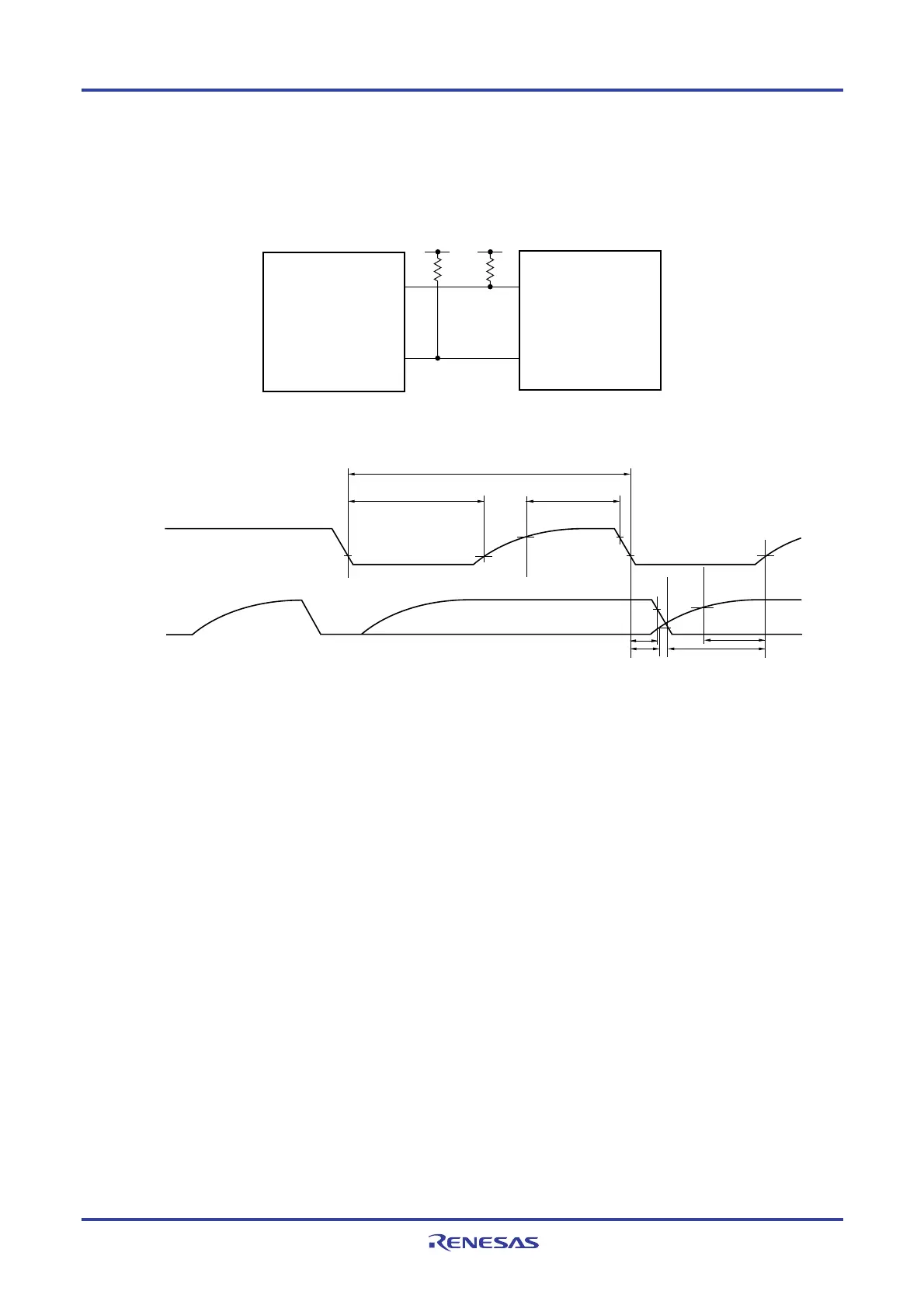

Simplified I

2

C mode serial transfer timing (during communication at different potential)

SDAr

t

LOW

tHIGH

tHD:DAT

SCLr

t

SU:DAT

1/fSCL

Caution Select the TTL input buffer and the N-ch open drain output (V

DD tolerance) mode for the SDAr pin and

the N-ch open drain output (V

DD tolerance) mode for the SCLr pin by using port input mode register g

(PIMg) and port output mode register g (POMg).

Remarks 1. R

b[Ω]:Communication line (SDAr, SCLr) pull-up resistance, Cb[F]: Communication line (SDAr, SCLr) load

capacitance, V

b[V]: Communication line voltage

2. r: IIC number (r = 00, 01, 10, 20, 30, 31), g: PIM, POM number (g = 0, 1, 4, 5, 8, 14)

3. f

MCK: Serial array unit operation clock frequency

(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n:

Channel number (mn = 00, 01, 02, 10, 12, 13)

4. V

IH and VIL below are observation points for the AC characteristics of the serial array unit when

communicating at different potentials in simplified I

2

C mode mode.

4.0 V ≤ EVDD0 ≤ 5.5 V, 2.7 V ≤ Vb ≤ 4.0 V: VIH = 2.2 V, VIL = 0.8 V

2.7 V ≤ EV

DD0 < 4.0 V, 2.3 V ≤ Vb ≤ 2.7 V: VIH = 2.0 V, VIL = 0.5 V

1.8 V ≤ EVDD0 < 3.3 V, 1.6 V ≤ Vb ≤ 2.0 V: VIH = 1.5 V, VIL = 0.32 V

<R>

Loading...

Loading...