RL78/G13 CHAPTER 15 DMA CONTROLLER

R01UH0146EJ0100 Rev.1.00 809

Sep 22, 2011

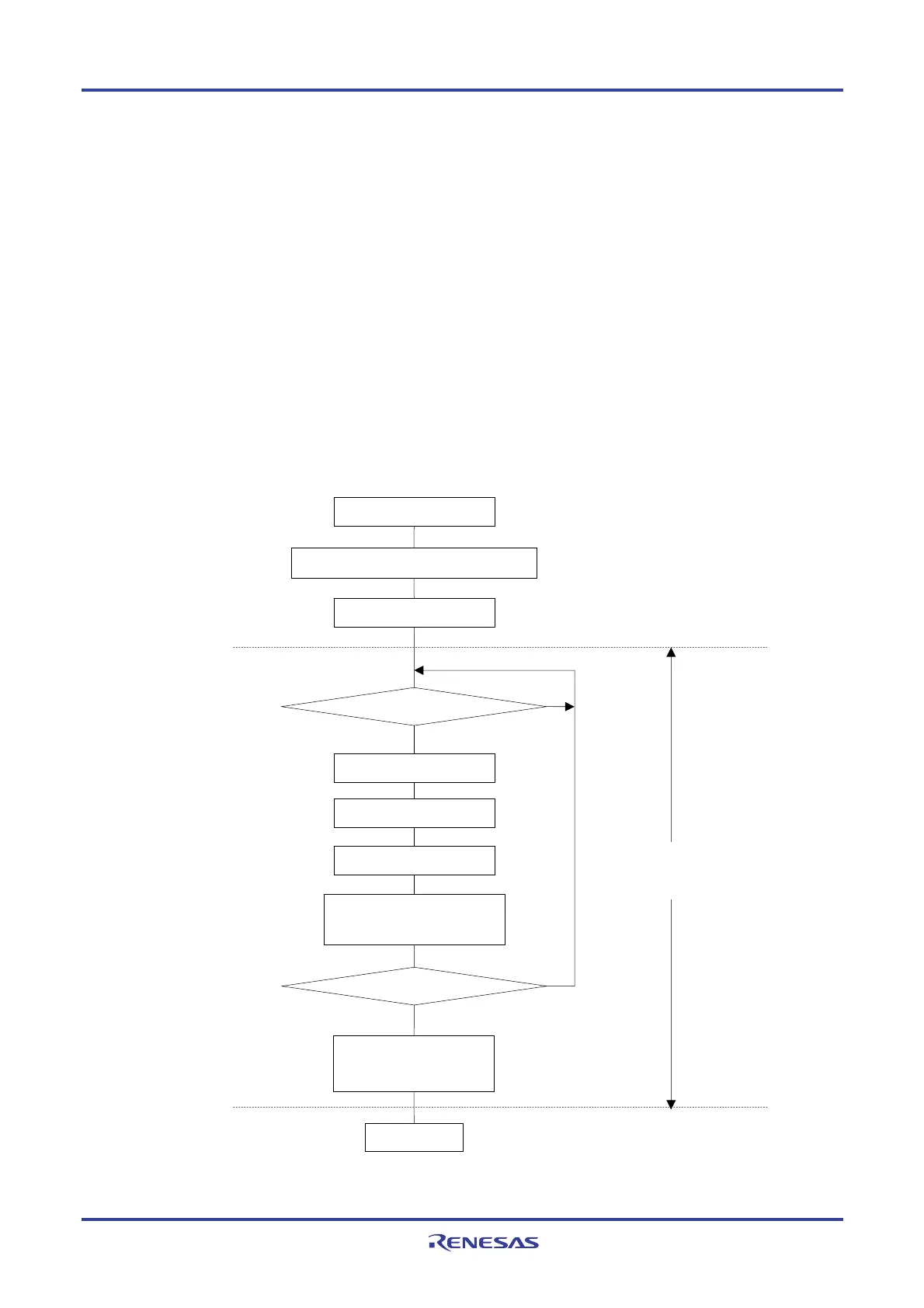

No

No

DSTn = 1

DSTn = 0

INTDMAn = 1

DMA trigger = 1?

DBCn = 0000H ?

Yes

Yes

DENn = 1

Setting DSAn, DRAn, DBCn, and DMCn

Transmitting DMA request

Receiving DMA acknowledge

DMA transfer

DRAn = DRAn + 1 (or + 2)

DBCn = DBCn − 1

DENn = 0

Set by software program

Operation by DMA

controller (hardware)

Set by software program

15.4 Operation of DMA Controller

15.4.1 Operation procedure

<1> The DMA controller is enabled to operate when DENn = 1. Before writing the other registers, be sure to set the

DENn bit to 1. Use 80H to write with an 8-bit manipulation instruction.

<2> Set an SFR address, a RAM address, the number of times of transfer, and a transfer mode of DMA transfer to

DMA SFR address register n (DSAn), DMA RAM address register n (DRAn), DMA byte count register n (DBCn),

and DMA mode control register n (DMCn).

<3> The DMA controller waits for a DMA trigger when DSTn = 1. Use 81H to write with an 8-bit manipulation

instruction.

<4> When a software trigger (STGn) or a start source trigger specified by the IFCn3 to IFCn0 bits is input, a DMA

transfer is started.

<5> Transfer is completed when the number of times of transfer set by the DBCn register reaches 0, and transfer is

automatically terminated by occurrence of an interrupt (INTDMAn).

<6> Stop the operation of the DMA controller by clearing the DENn bit to 0 when the DMA controller is not used.

Figure 15-6. Operation Procedure

Remark n: DMA channel number (n = 0 to 3)

Loading...

Loading...