RL78/G13 CHAPTER 12 SERIAL ARRAY UNIT

R01UH0146EJ0100 Rev.1.00 657

Sep 22, 2011

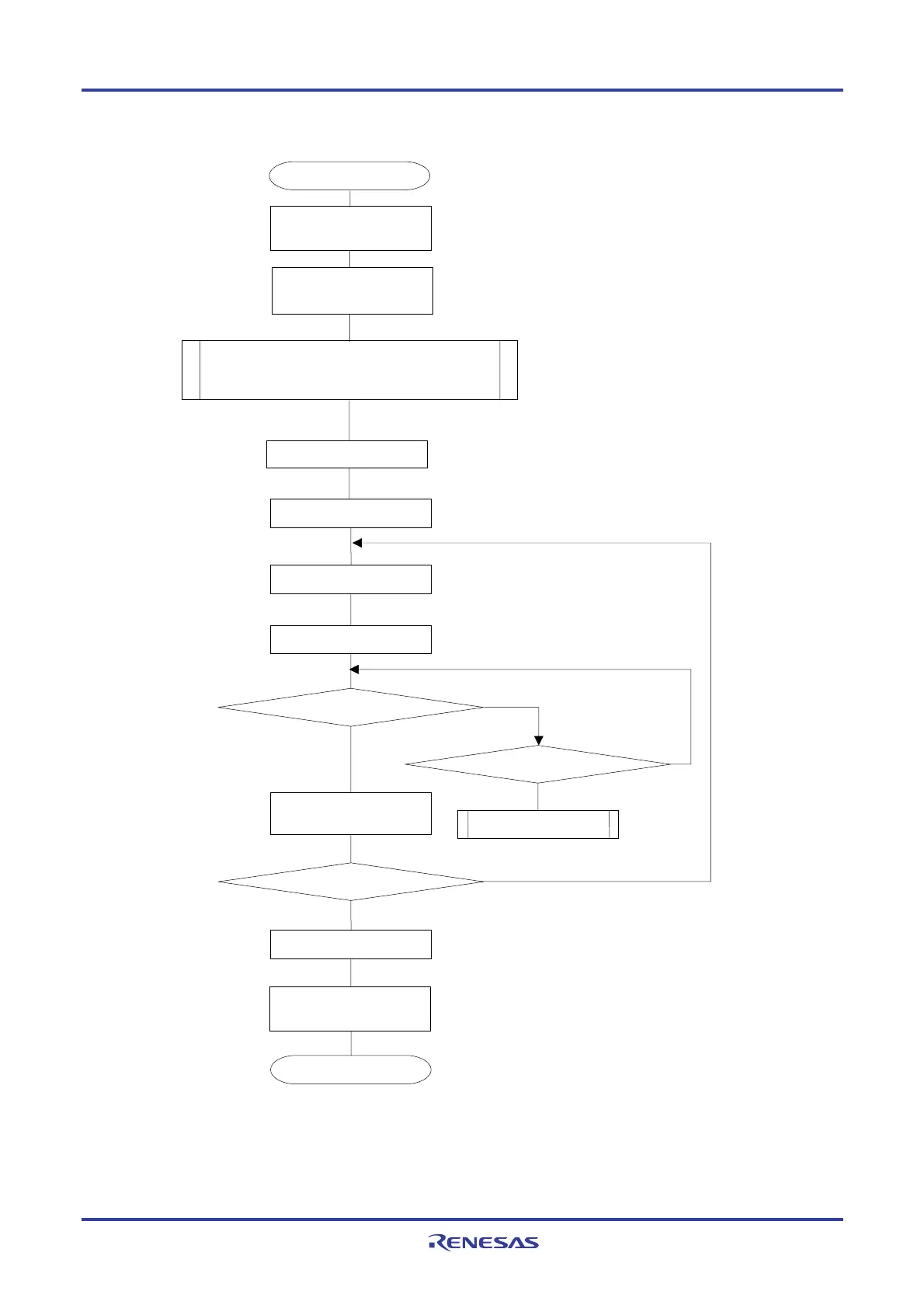

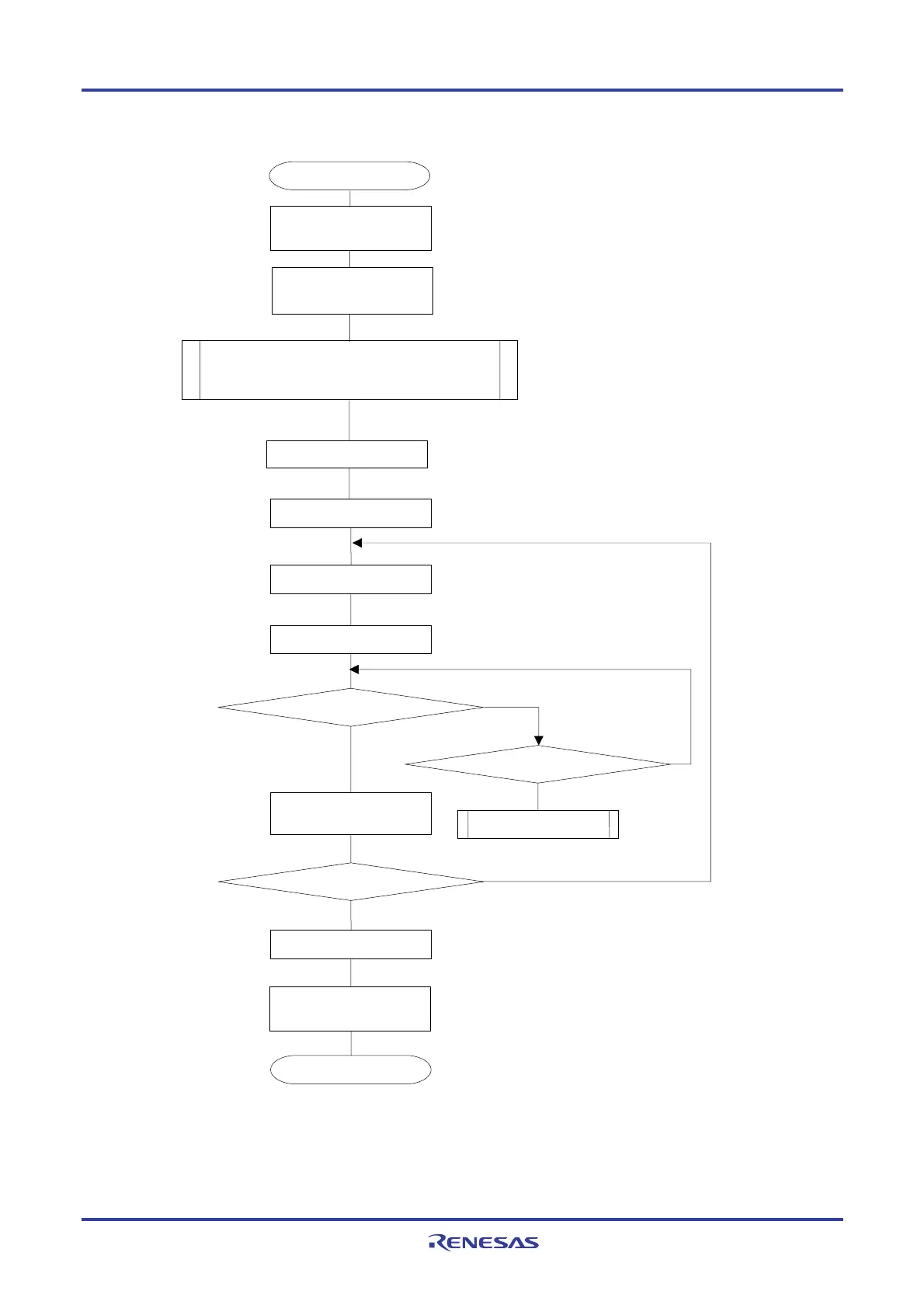

Figure 12-90. Flowchart of UART Reception

Note In case of 9-bit of data, be sure to read SDRmn [8:0] and not the RxDq register.

Caution Set the RXEmn bit of SCRmn to 1, and then be sure to set SSmn = 1 after 4 or more f

CLK clocks

have elapsed.

Starting UART communication

Writing 1 to the SSmn bit

Writing 1 to the STmn bit

End of UART communication

Specify the initial settings

while the SEmn bit of serial

channel enable status register

m (SEm) is 0 (operation is

stopped).

SMRmn, SMRmr, SCRmn: Setting communication

SDRmn[15:9]: Setting transfer rate

Transfer end interrupt

generated?

Reception completed?

No

No

Yes

Yes

Starting reception

Reading the RXDq register

(SDRmn[7:0])

Note

Detecting start bit

Error interrupt generated?

Error processing

No

Yes

Port manipulation

Clearing the SAUmEN bit of the

PER0 register to 0

Setting the SAUmEN bit of the

PER0 register to 1

Setting transfer rate by the

SPSm register

Loading...

Loading...