RL78/G13 CHAPTER 20 POWER-ON-RESET CIRCUIT

R01UH0146EJ0100 Rev.1.00 886

Sep 22, 2011

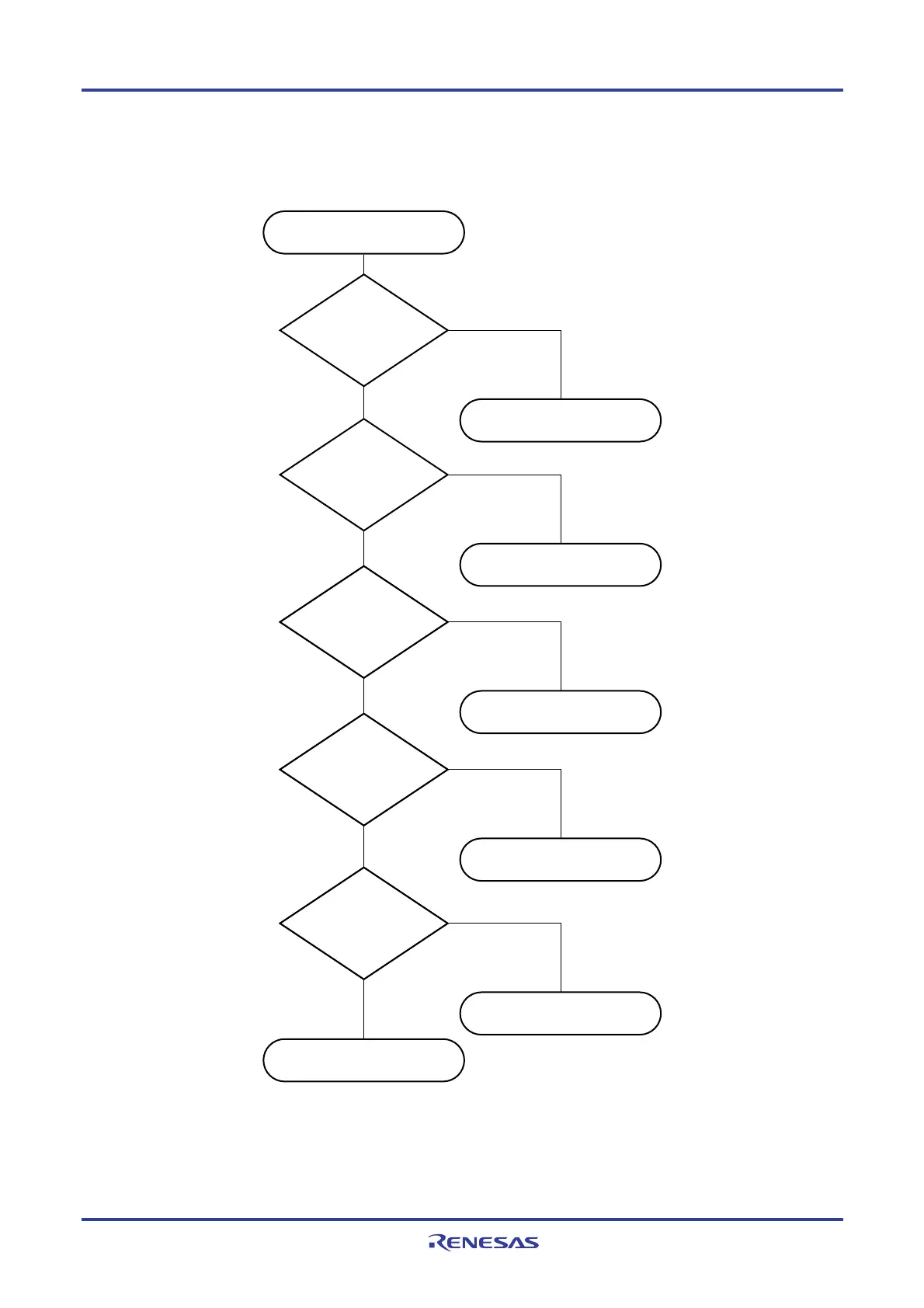

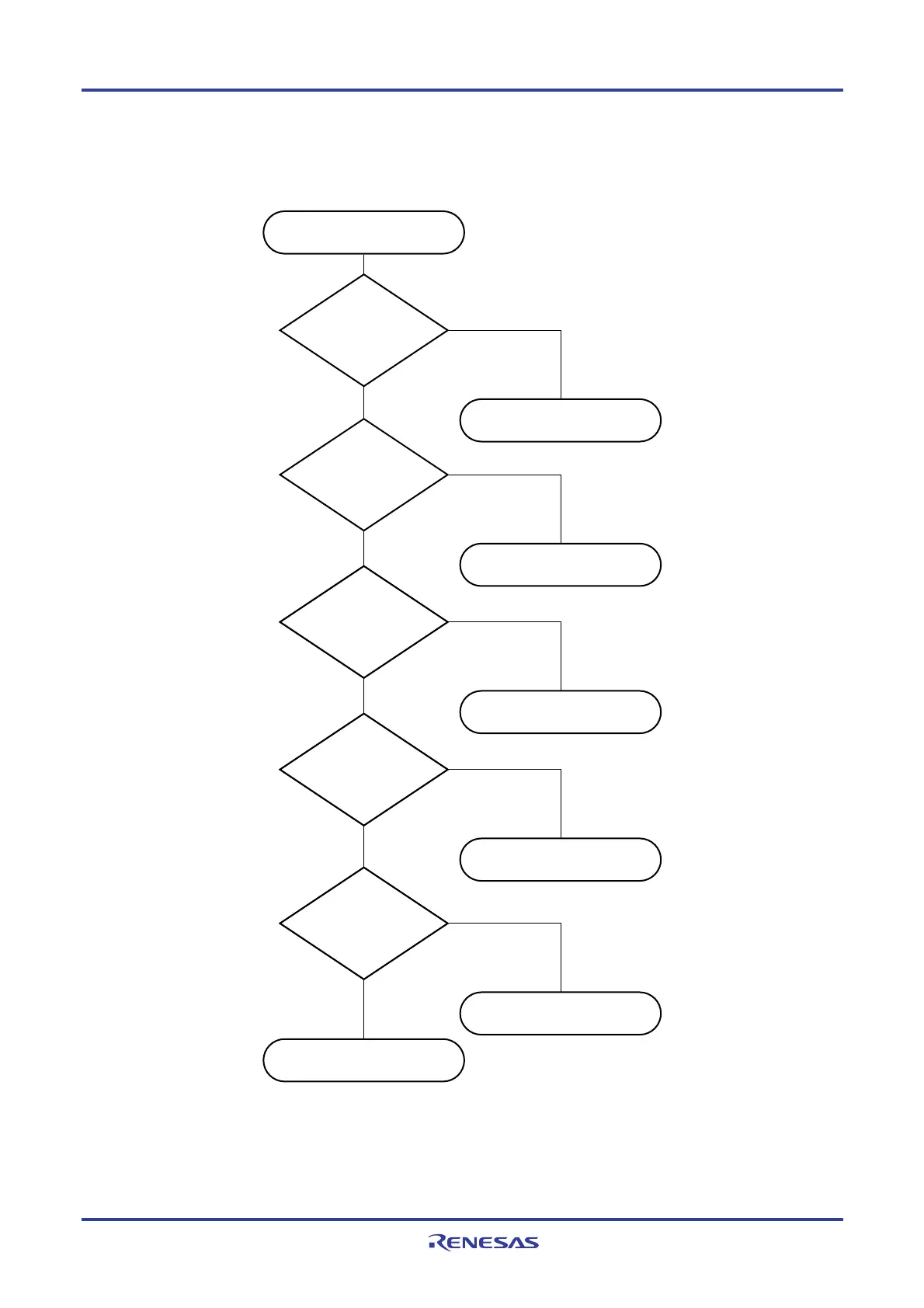

Figure 20-3. Example of Software Processing After Reset Release (2/2)

• Checking reset source

Yes

No

No

Check reset source

Power-on-reset/external

reset generated

Reset processing by

watchdog timer

Reset processing by

voltage detector

No

WDTRF of RESF

register = 1?

Yes

No

Reset processing by

illegal instruction execution

Note

TRAP of RESF

register = 1?

Yes

Reset processing by

RAM parity error

Yes

LVIRF of RESF

register = 1?

RPERF of RESF

register = 1?

No

Reset processing by

illegal-memory access

Yes

IAWRF of RESF

register = 1?

Note The illegal instruction is generated when instruction code FFH is executed.

Reset by the illegal instruction execution not issued by emulation with the in-circuit emulator or on-chip

debug emulator.

Loading...

Loading...