Controller area network (bxCAN) UM0306

314/519

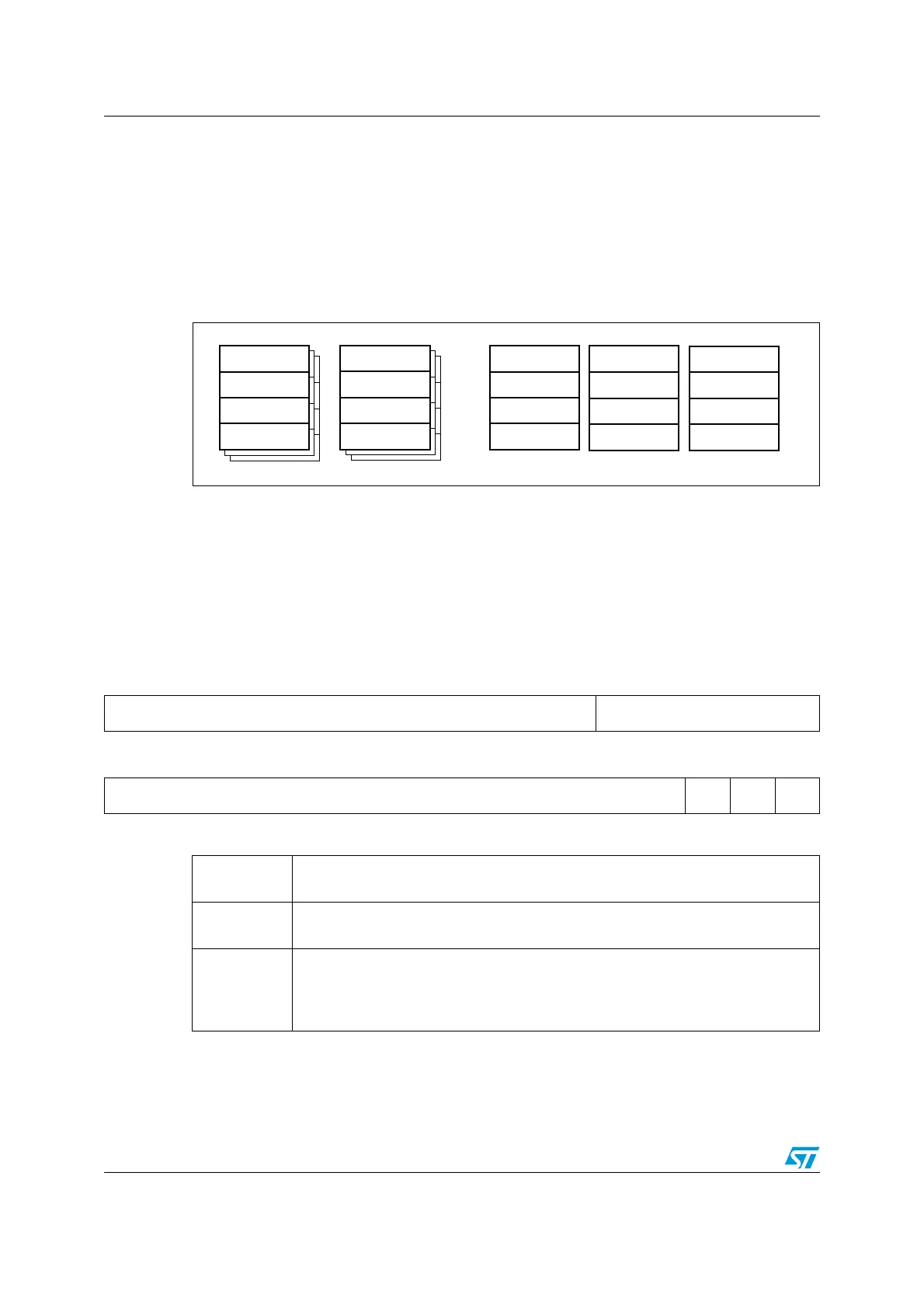

Transmit and receive mailboxes have the same registers except:

● The FMI field in the CAN_RDTxR register.

● A receive mailbox is always write protected.

● A transmit mailbox is write-enabled only while empty, corresponding TME bit in the

CAN_TSR register set.

There are 3 TX Mailboxes and 2 RX Mailboxes. Each RX Mailbox allows access to a 3 level

depth FIFO, the access being offered only to the oldest received message in the FIFO.

Each mailbox consist of 4 registers.

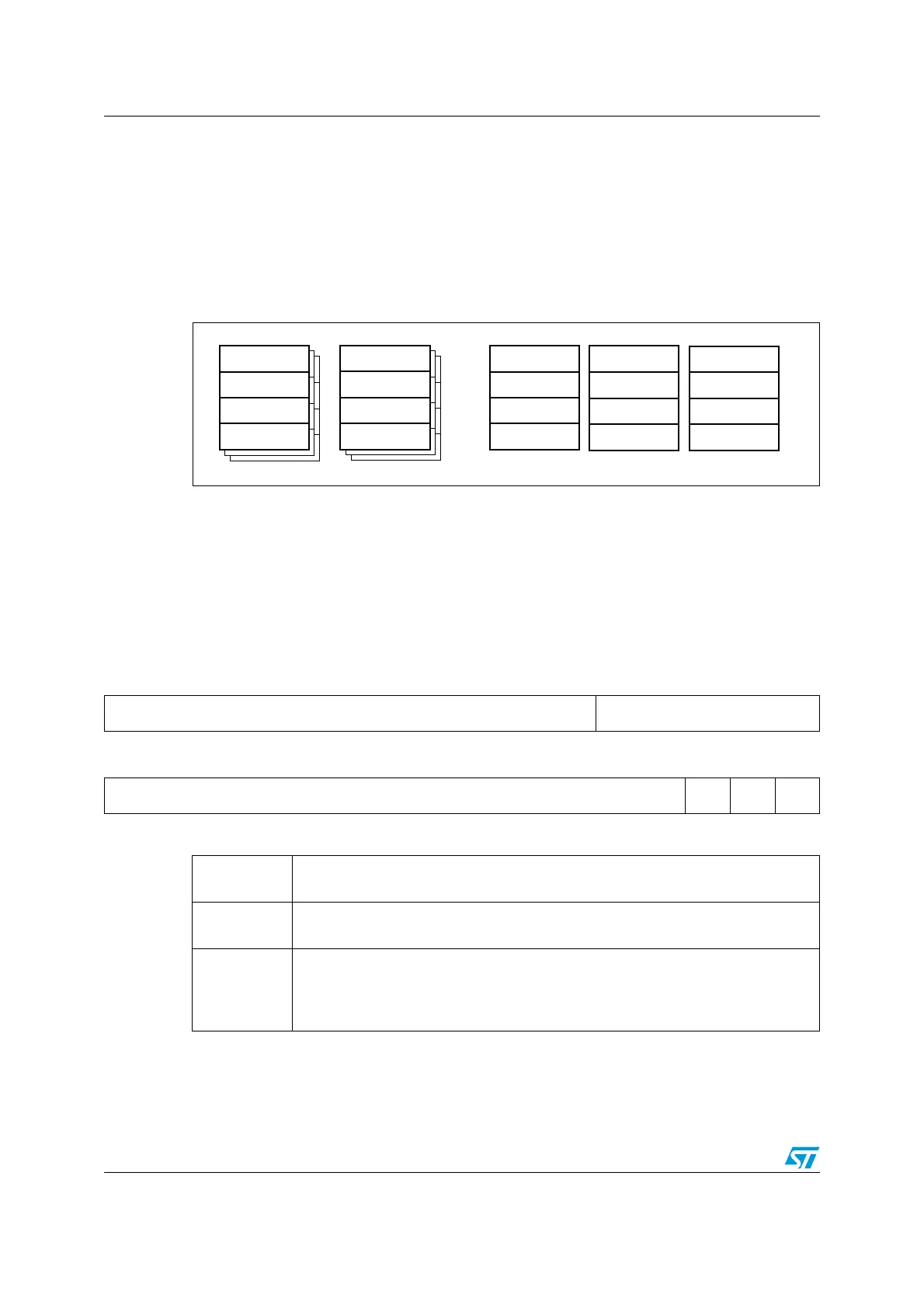

TX mailbox identifier register (CAN_TIxR) (x=0..2)

Address Offsets: 180h, 190h, 1A0h

Reset Value: xXh (except bit 0, TXRQ = 0)

Note: 1 All TX registers are write protected when the mailbox is pending transmission (TMEx reset).

2 This register also implements the TX request control (bit 0) - reset value 0.

CAN_RI0R

CAN_RDT0R

CAN_RL0R

CAN_RH0R

CAN_TI0R

CAN_TDT0R

CAN_TDL0R

CAN_TDH0R

FIFO0

Three Tx Mailboxes

CAN_RI1R

CAN_RDT1R

CAN_RL1R

CAN_RH1R

FIFO1

CAN_TI1R

CAN_TDT1R

CAN_TDL1R

CAN_TDH1R

CAN_TI2R

CAN_TDT2R

CAN_TDL2R

CAN_TDH2R

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

STID[10:0] EXID[17:13]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

EXID[12:0] IDE RTR TXRQ

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:21

STID[10:0]: Standard Identifier

The standard part of the identifier.

Bit 20:3

EXID[17:0:] Extended Identifier

The extended part of the identifier.

Bit 2

IDE: Extended Identifier

This bit defines the identifier type of message in the mailbox.

0: Standard identifier.

1: Extended identifier.

Loading...

Loading...