UM0306 Reset and clock control (RCC)

57/519

4.3.3 Clock interrupt register (RCC_CIR)

Address offset: 08h

Reset value: 0000 0000h

Access: no wait state, word, half-word and byte access

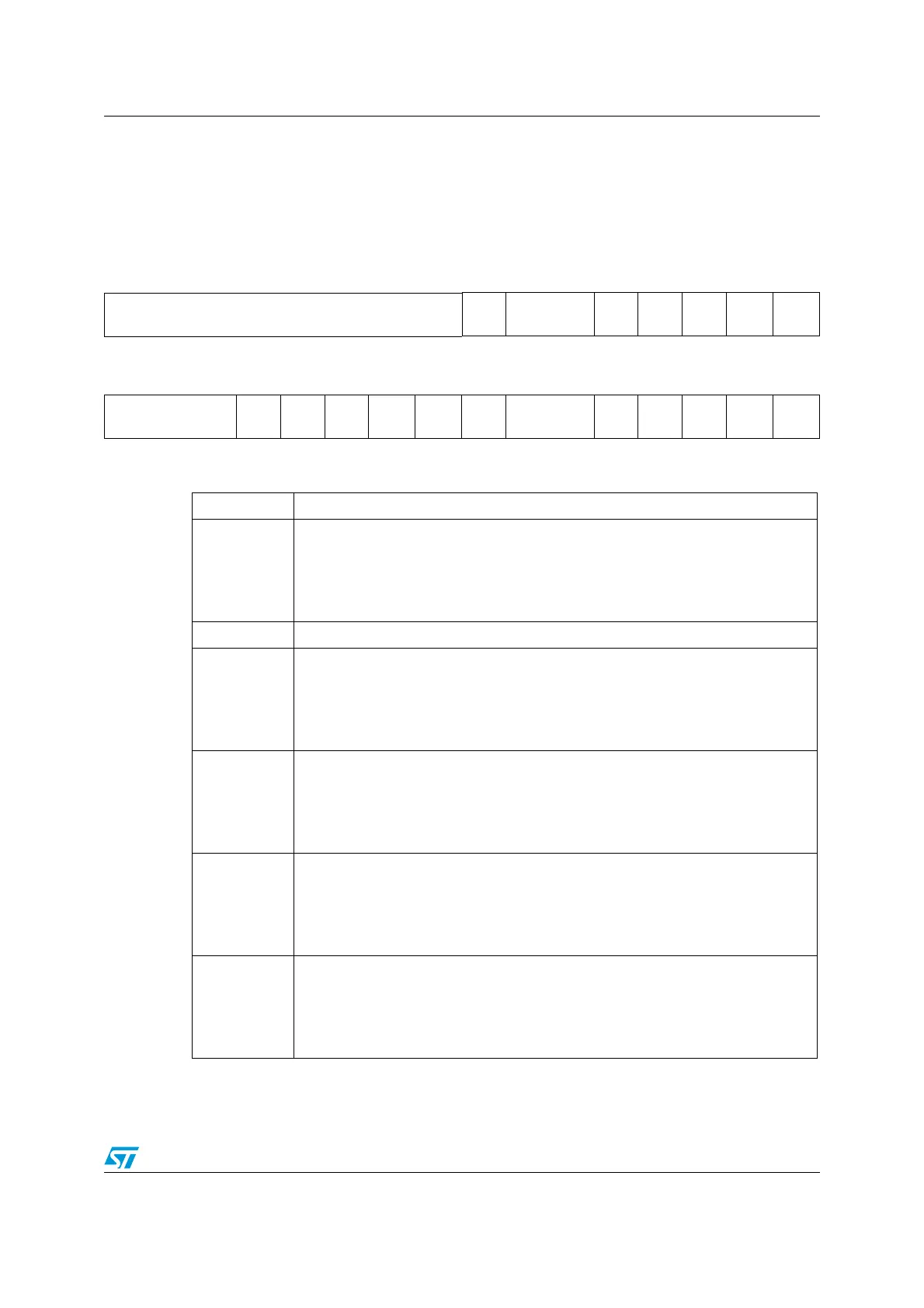

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

CSSC Reserved

PLL

RDYC

HSE

RDYC

HSI

RDYC

LSE

RDYC

LSI

RDYC

w wwww w

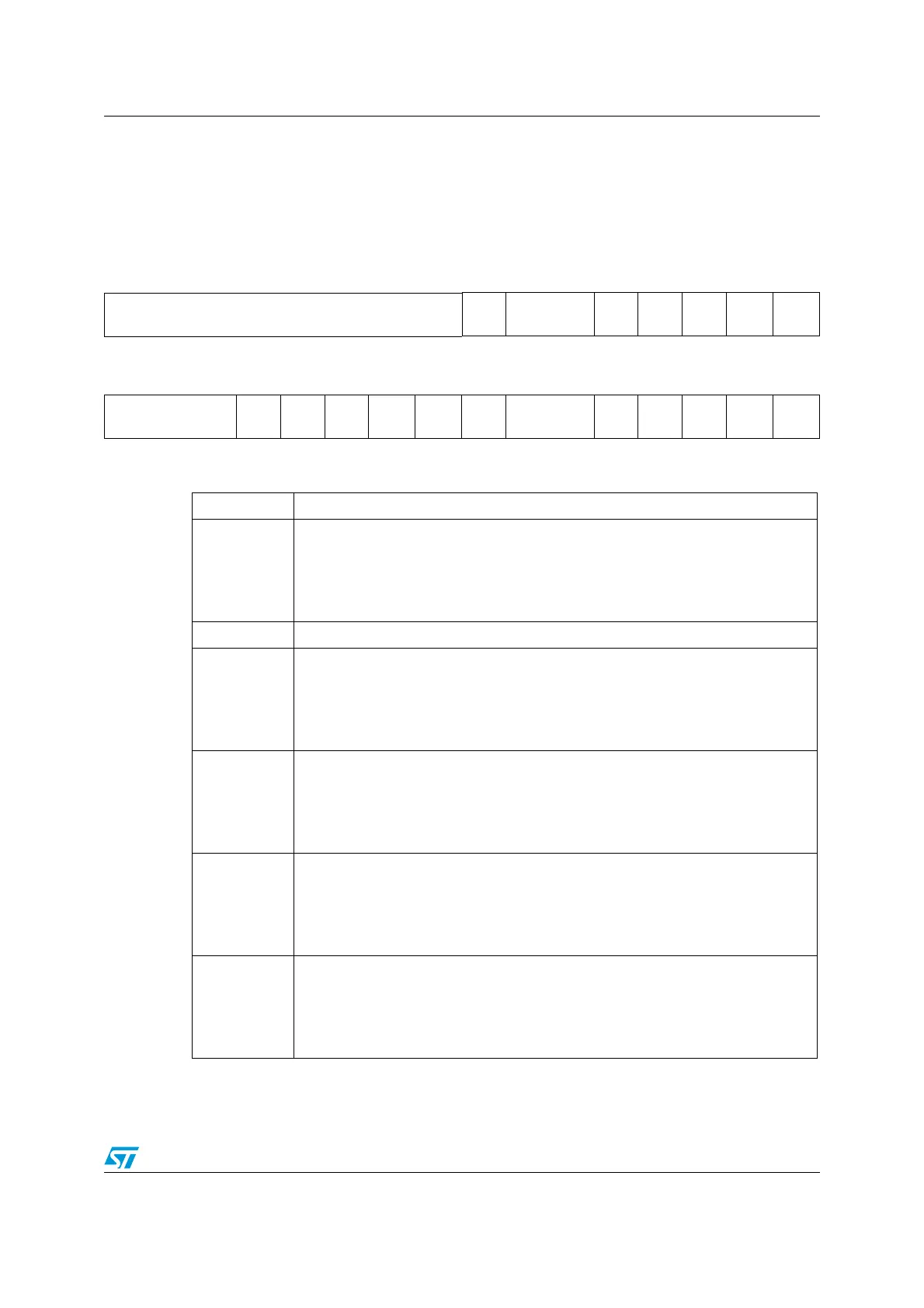

1514131211109 87654321 0

Reserved

PLL

RDYIE

HSE

RDYIE

HSI

RDYIE

LSE

RDYIE

LSI

RDYIE

CSSF Reserved

PLL

RDYF

HSE

RDYF

HSI

RDYF

LSE

RDYF

LSI

RDYF

rw rw rw rw rw r r r r r r

Bits 31:24 Reserved, always read as 0.

Bit 23

CSSC Clock Security System Interrupt Clear

Set by software to clear CSSF.

Reset by hardware when clear done.

0: CSSF not cleared

1: CSSF cleared

Bits 22:21 Reserved, always read as 0.

Bit 20

PLLRDYC PLL Ready Interrupt Clear

Set by software to clear PLLRDYF.

Reset by hardware when clear done.

0: PLLRDYF not cleared

1: PLLRDYF cleared

Bit 19

HSERDYC HSE Ready Interrupt Clear

Set by software to clear HSERDYF.

Reset by hardware when clear done.

0: HSERDYF not cleared

1: HSERDYF cleared

Bit 18

HSIRDYC HSI Ready Interrupt Clear

Set by software to clear HSIRDYF.

Reset by hardware when clear done.

0: HSIRDYF not cleared

1: HSIRDYF cleared

Bit 17

LSERDYC LSE Ready Interrupt Clear

Set by software to clear LSERDYF.

Reset by hardware when clear done.

0: LSERDYF not cleared

1: LSERDYF cleared

Loading...

Loading...