UM0306 Power control (PWR)

41/519

3.4 Power control registers

3.4.1 Power control register (PWR_CR)

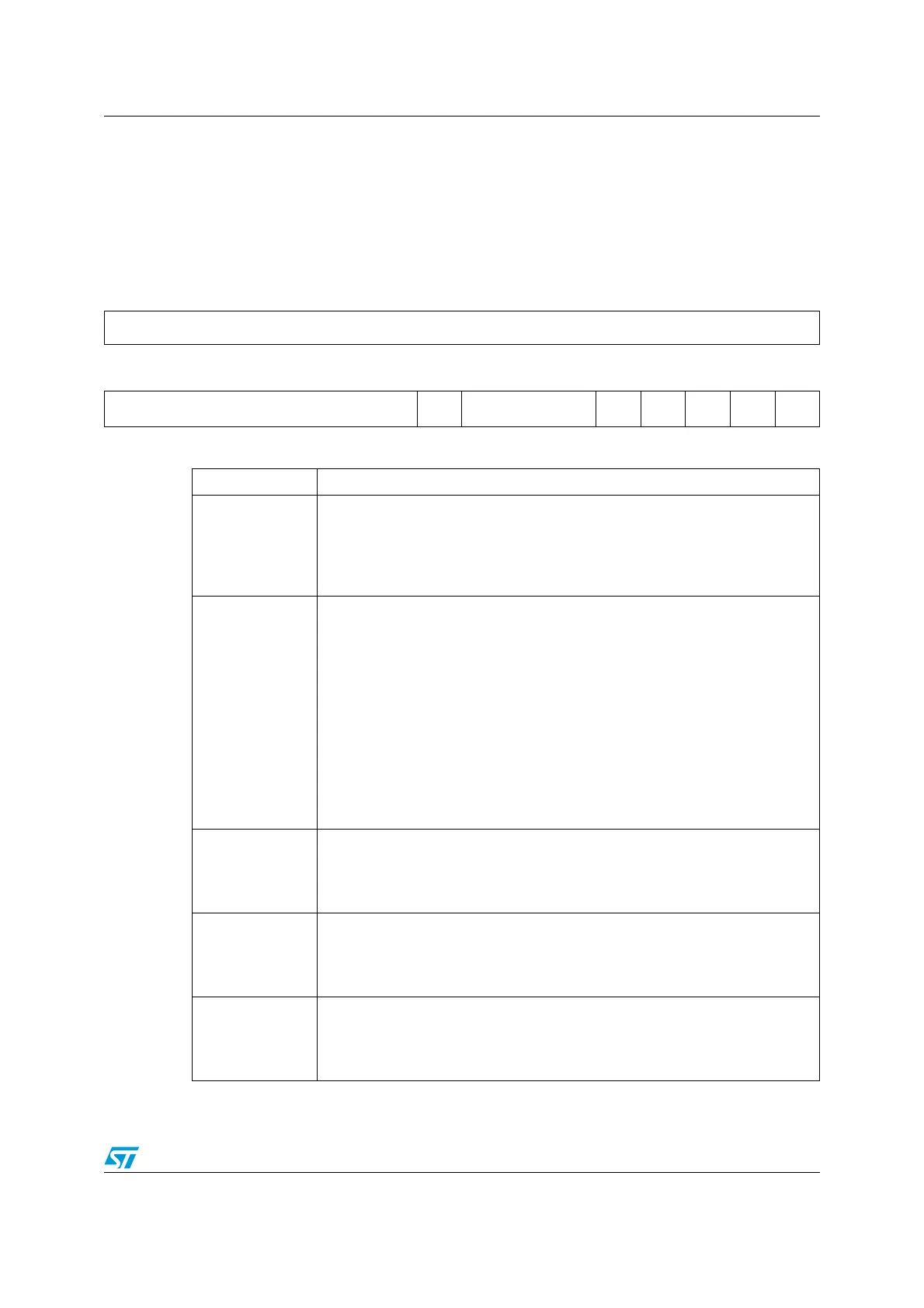

Address Offset: 00h

Reset Value: 0000 0000 0000 0000 (0000h) (reset by wake-up from STANDBY mode)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

DBP PLS[2:0] PVDE CSBF CWUF PDDS LPDS

rw rw rw rw rw rc_w1 rc_w1 rw rw

Bits 31:9 Reserved, always read as 0.

Bit 8

DBP: Disable Backup Domain write protection.

In reset state, the RTC and backup registers are protected against parasitic

write access. This bit must be set to enable write access to these registers.

0: Access to RTC and Backup registers disabled

1: Access to RTC and Backup registers enabled

Bits 7:5

PLS[2:0]: PVD Level Selection.

These bits are written by software to select the voltage threshold detected by

the Power Voltage Detector

000: 2.2V

001: 2.3V

010: 2.4V

011: 2.5V

100: 2.6V

101: 2.7V

110: 2.8V

111: 2.9V

Note: Refer to the electrical characteristics of the datasheet for more details.

Bit 4

PVDE: Power Voltage Detector Enable.

This bit is set and cleared by software.

0: PVD disabled

1: PVD enabled

Bit 3

CSBF: Clear STANDBY Flag.

This bit is always read as 0.

0: No effect

1: Clear the SBF Standby Flag (write).

Bit 2

CWUF: Clear Wake-up Flag.

This bit is always read as 0.

0: No effect

1: Clear the WUF Wake-up Flag after 2 System clock cycles. (write)

Loading...

Loading...