UM0306 Reset and clock control (RCC)

47/519

Each clock source can be switched on or off independently when it is not used, to optimize

power consumption.

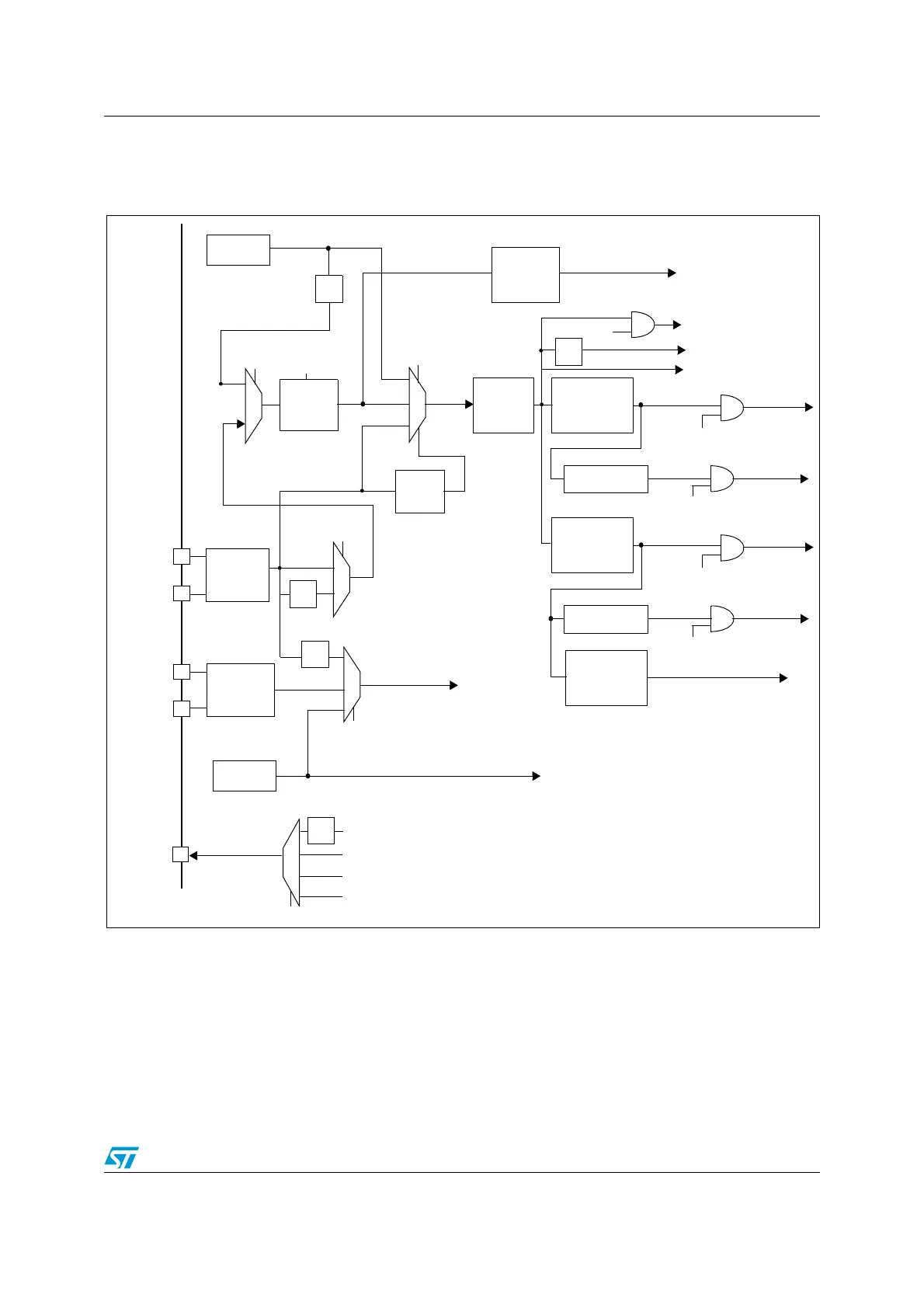

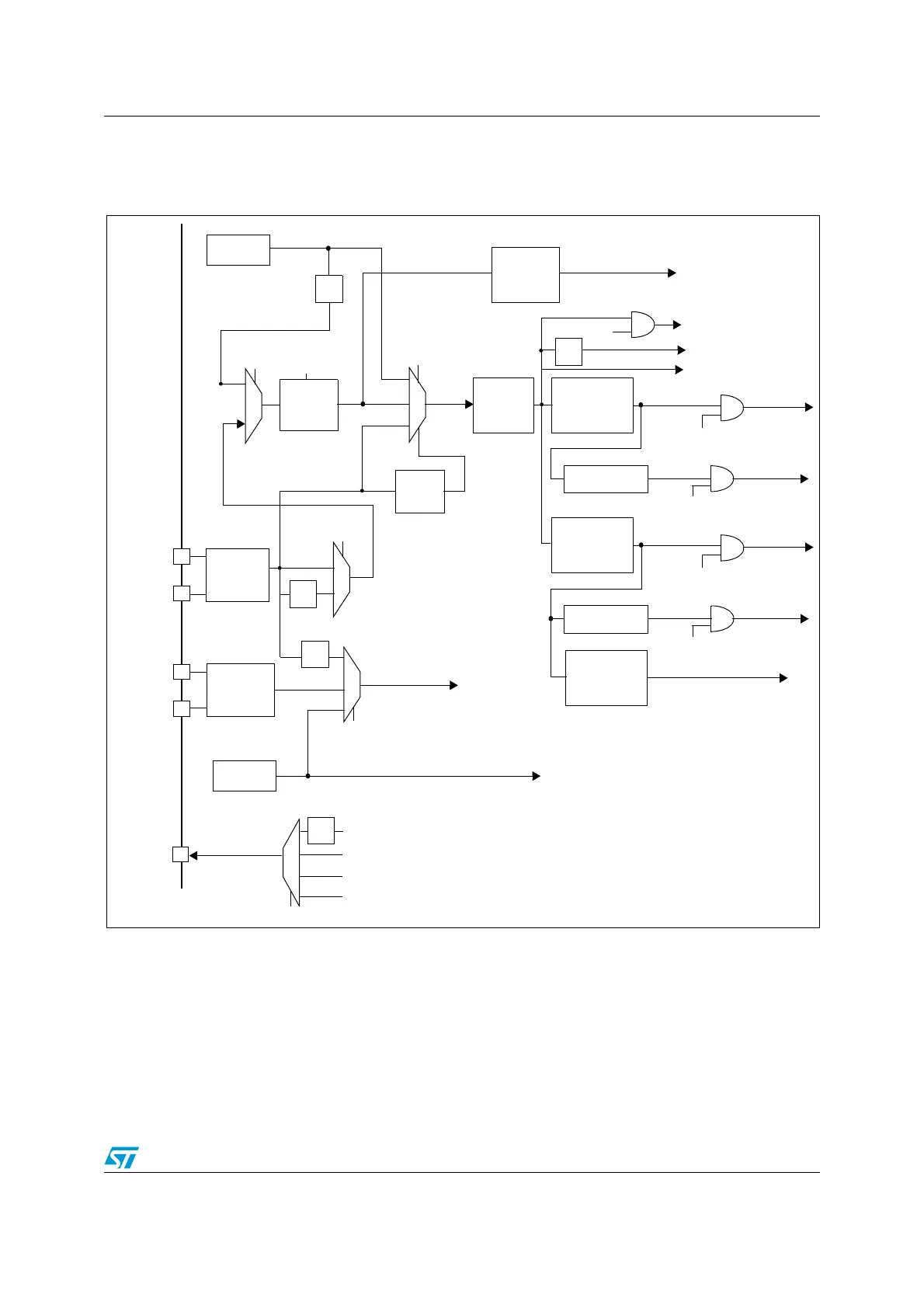

Figure 7. Clock tree

Several prescalers allow the configuration of the AHB frequency, the high speed APB

(APB2) and the low speed APB (APB1) domains. The AHB and the APB2 domains

maximum frequency is 72 MHz. The APB1 domains maximum allowed frequency is 36

MHz. The RCC feeds the Cortex System Timer (SysTick) external clock with the AHB clock

divided by 8. The SysTick can work either with this clock or with the Cortex clock (AHB),

configurable in the SysTick Control and Status Register. The ADCs are clocked by the clock

of the High Speed domain (APB2) divided by 2, 4, 6 or 8.

HSE OSC

4-16 MHz

OSC_IN

OSC_OUT

OSC32_IN

OS32_OUT

LSE OSC

32.768 kHz

HSI RC

8 MHz

LSI RC

32 kHz

to Independent Watchdog (IWDG)

PLL

x2, x3, x4

PLLMUL

HSE = High Speed External clock signal

LSE = Low Speed External clock signal

LSI = Low Speed Internal clock signal

HSI = High Speed Internal clock signal

Legend:

MCO

Clock Output

Main

PLLXTPRE

/2

..., x16

AHB

Prescaler

/1, 2 ..512

/2

PLLCLK

HSI

HSE

APB1

Prescaler

/1, 2, 4, 8, 16

ADC

Prescaler

/2, 4, 6, 8

ADCCLK

PCLK1

HCLK

PLLCLK

to AHB bus, core,

memory and DMA

TIM2, 3, 4

x1, 2 Multiplier

USBCLK

to USB interface

to TIM2, 3

and 4

USB

Prescaler

/1, 1.5

to ADC

LSE

LSI

HSI

/128

/2

HSI

HSE

peripherals

to APB1

Peripheral Clock

Enable (13 bits)

Enable (3 bits)

Peripheral Clock

APB2

Prescaler

/1, 2, 4, 8, 16

PCLK2

TIM1 Timer

x1, 2 Multiplier

to TIM1

peripherals

to APB2

Peripheral Clock

Enable (11 bits)

Enable (1 bit)

Peripheral Clock

48 MHz

72 MHz max

72 MHz

72 MHz max

36 MHz max

to RTC

PLLSRC

SW

MCO

CSS

to Cortex System timer

/8

Clock

Enable (3 bits)

SYSCLK

max

RTCCLK

RTCSEL[1:0]

TIM1CLK

TIMXCLK

IWDGCLK

SYSCLK

FCLK Cortex

free running clock

Loading...

Loading...