Reset and clock control (RCC) UM0306

64/519

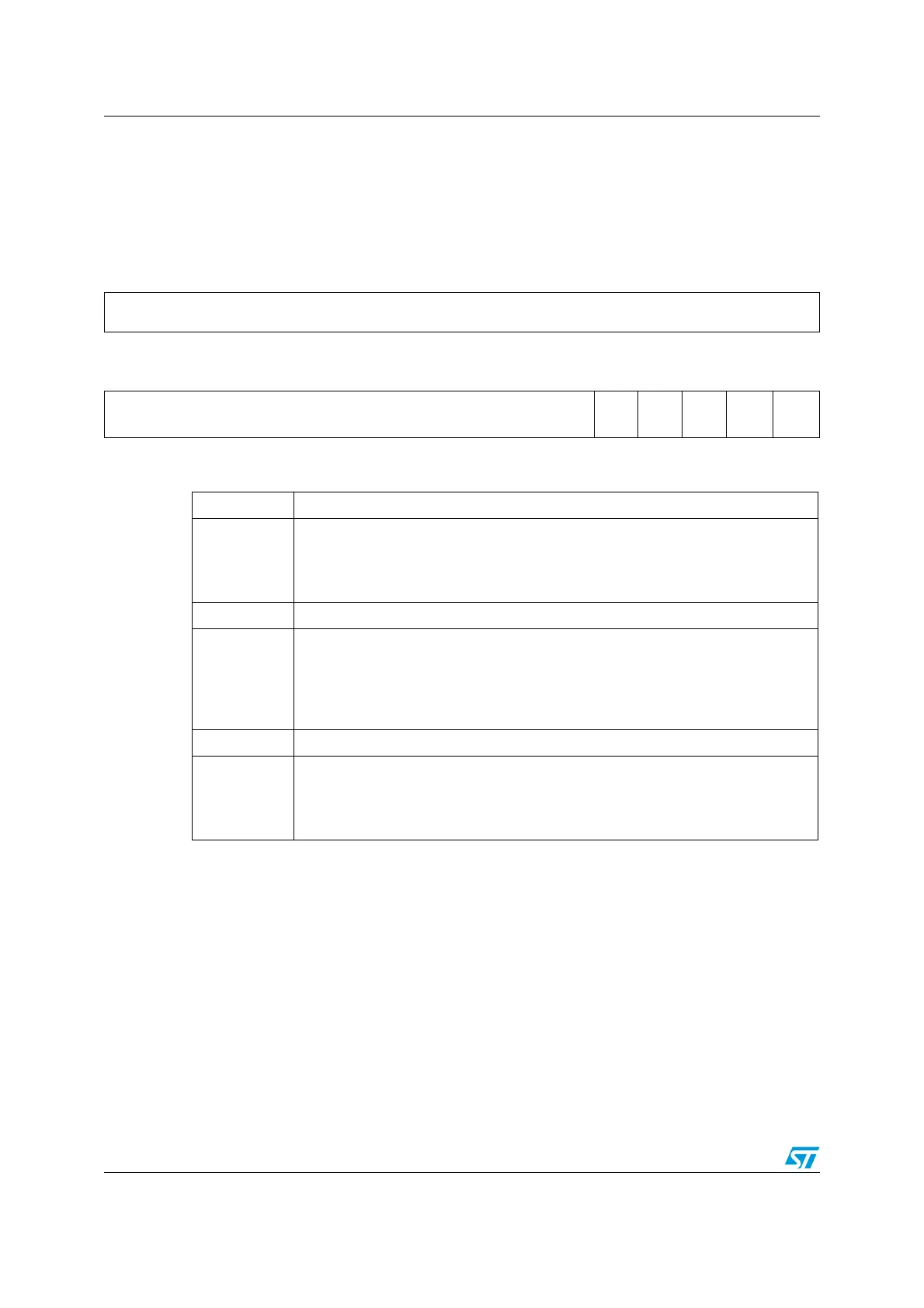

4.3.6 AHB Peripheral Clock enable register (RCC_AHBENR)

Address offset: 14h

Reset value: 0000 0014h

Access: no wait state, word, half-word and byte access

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109 87654321 0

Reserved

FLITF

EN

Res.

SRAM

EN

Res.

DMA

EN

rw rw rw

Bits 31:5 Reserved, always read as 0.

Bit 4

FLITFEN FLITF clock enable

Set and reset by software to disable/enable FLITF clock during sleep mode.

0: FLITF clock disabled during SLEEP mode

1: FLITF clock enabled during SLEEP mode

Bit 3 Reserved, always read as 0.

Bit 2

SRAMEN SRAM interface clock enable

Set and reset by software to disable/enable SRAM interface clock during SLEEP

mode.

0: SRAM interface clock disabled during SLEEP mode.

1: SRAM interface clock enabled during SLEEP mode

Bit 1 Reserved, always read as 0.

Bit 0

DMAEN DMA clock enable

Set and reset by software.

0: DMA clock disabled

1: DMA clock enabled

Loading...

Loading...