Analog/digital converter (ADC) UM0306

482/519

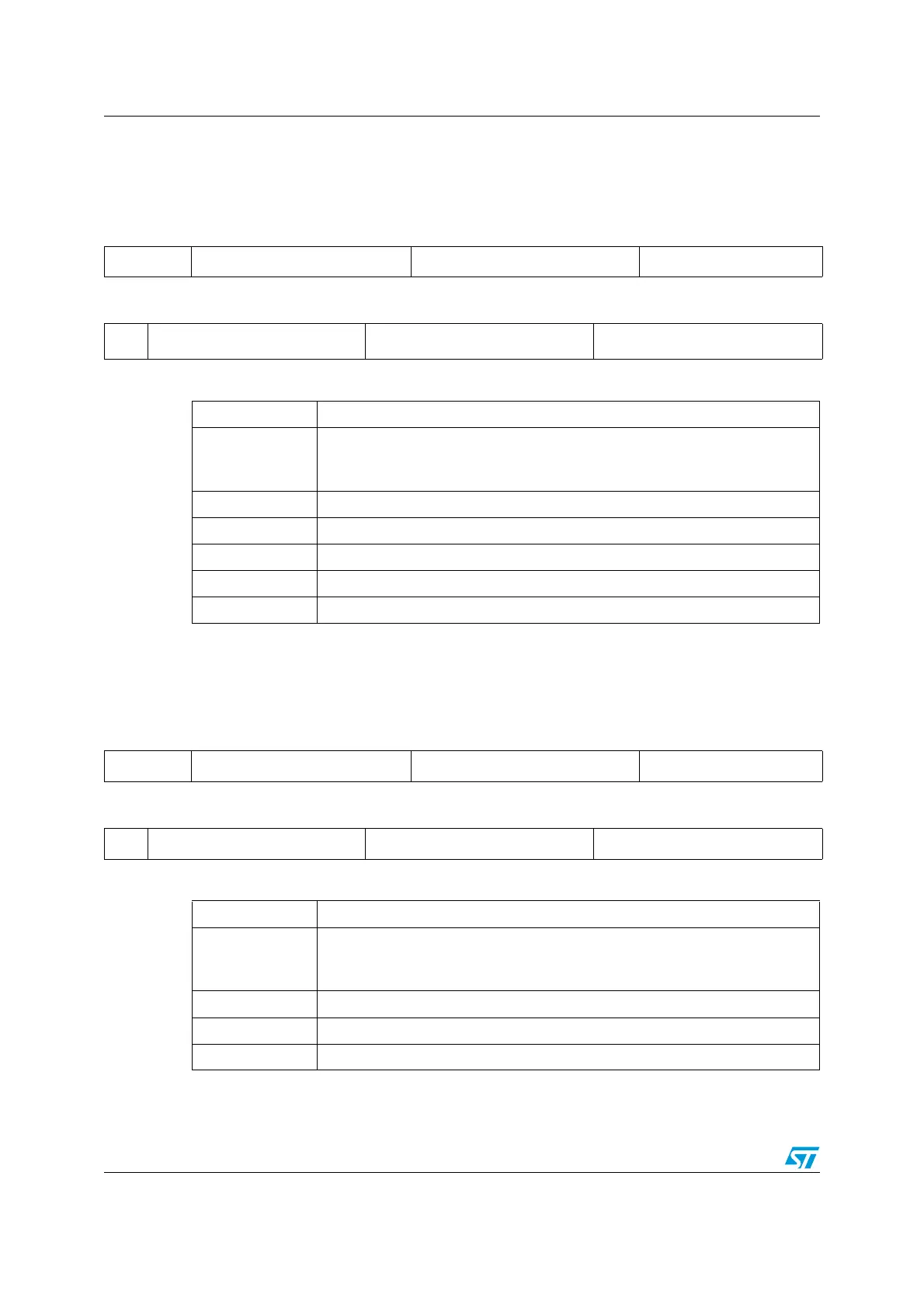

19.13.10 ADC regular sequence register 2 (ADC_SQR2)

Address offset: 30h

Reset value: 0000 0000h

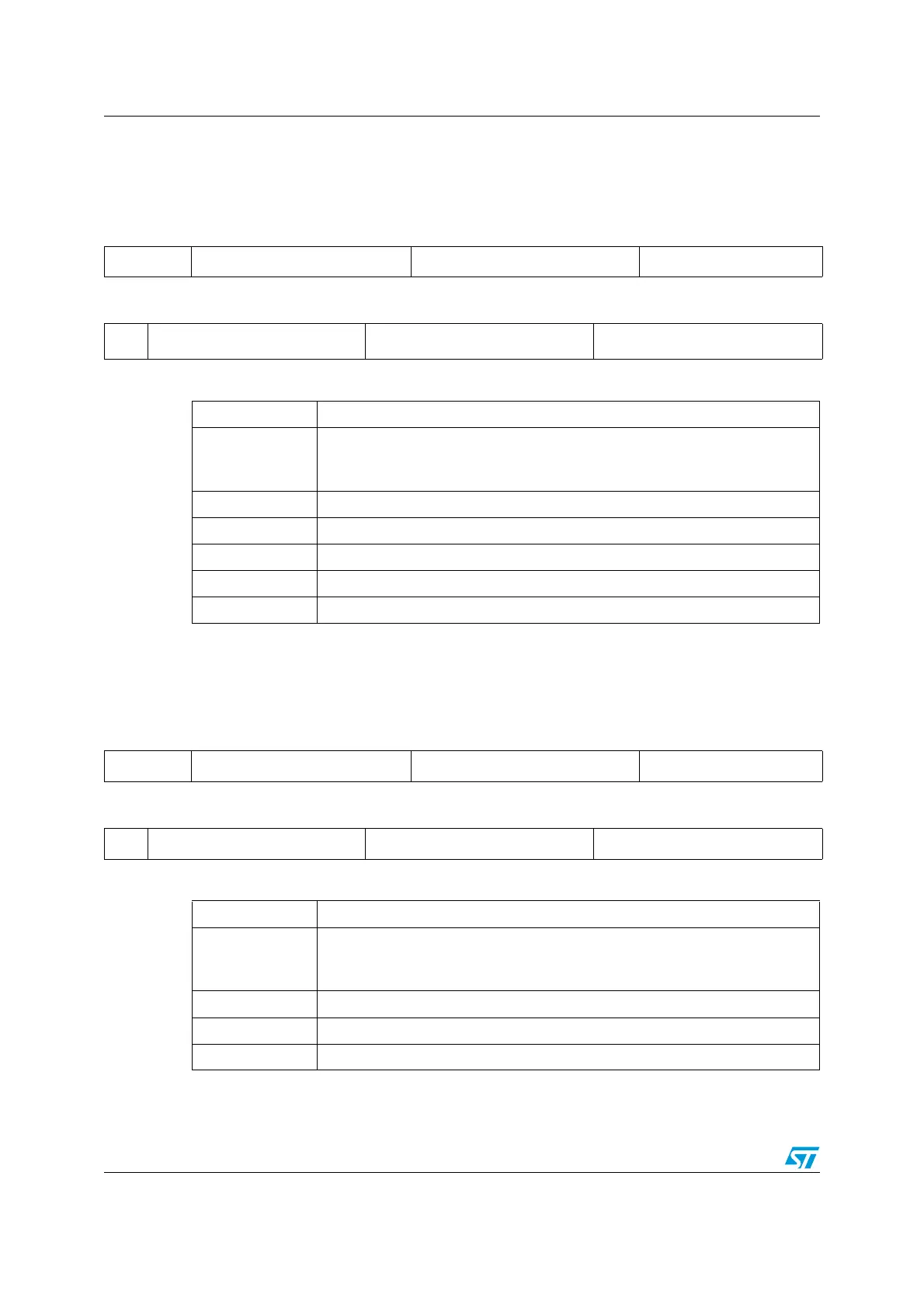

19.13.11 ADC regular sequence register 3 (ADC_SQR3)

Address offset: 34h

Reset value: 0000 0000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved SQ12[4:0] SQ11[4:0] SQ10[4:1]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

SQ10_

0

SQ9[4:0] SQ8[4:0] SQ7[4:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:30 Reserved, must be kept cleared.

Bits 29:26

SQ12[4:0]: 12th conversion in regular sequence

These bits are written by software with the channel number (0..17) assigned as

the 12th in the sequence to be converted.

Bits 24:20 SQ11[4:0]: 11th conversion in regular sequence

Bits 19:15 SQ10[4:0]: 10th conversion in regular sequence

Bits 14:10 SQ9[4:0]: 9th conversion in regular sequence

Bits 9:5 SQ8[4:0]: 8th conversion in regular sequence

Bits 4:0 SQ7[4:0]: 7th conversion in regular sequence

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved SQ6[4:0] SQ5[4:0] SQ4[4:1]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

SQ4_0 SQ3[4:0] SQ2[4:0] SQ1[4:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:30 Reserved, must be kept cleared.

Bits 29:25

SQ6[4:0]: 6th conversion in regular sequence

These bits are written by software with the channel number (0..17) assigned

as the 6th in the sequence to be converted.

Bits 24:20 SQ5[4:0]: 5th conversion in regular sequence

Bits 19:15 SQ4[4:0]: 4th conversion in regular sequence

Bits 14:10 SQ3[4:0]: 3rd conversion in regular sequence

Loading...

Loading...