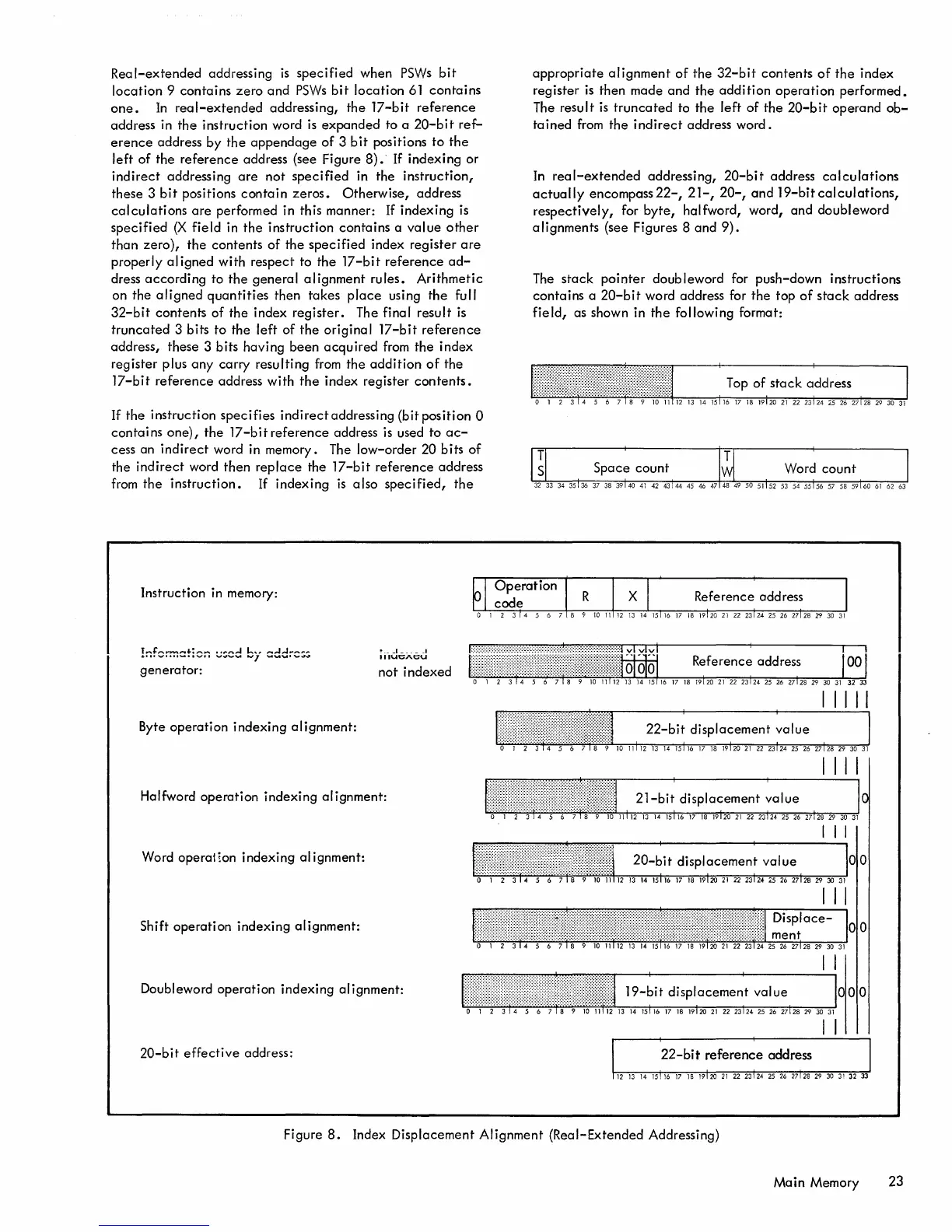

Real-extended

addressing

is

specified

when

PSWs

bit

location 9 contains

zero

and

PSWs

bit

location

61

contains

one.

In

real-extended

addressing, the

17-bit

reference

address in the instruction word

is

expanded to a

20-bit

ref-

erence

address by the

appendage

of

3

bit

positions

to

the

left of the reference address (see Figure

8).

If indexing or

indirect

addressing

are

not

specified

in the instruction,

these 3

bit

positions

contain

zeros.

Otherwise, address

calculations

are

performed in this manner:

If

indexing

is

specified

(X

field in the instruction contains a

value

other

than zero), the contents

of

the

specified

index register

are

properly al igned with respect to the

17-bit

reference

ad-

dress

according

to

the

general

alignment

rules. Arithmetic

on the

aligned

quantities

then takes

place

using the full

32-bit

contents of the index

register.

The fina I resul t

is

truncated

3 bits to the left

of

the

original

17-bit

reference

address, these 3 bits having been

acquired

from

the index

register plus any carry resulting

from

the

addition

of

the

17-bit

reference

address with

the

index register

contents.

If

the instruction specifies

indirect

addressing (bit position 0

contains one),

the

17-bit

reference

address

is

used to

ac-

cess an

indirect

word in memory. The low-order 20 bits

of

the

indirect

word then

replace

the

17-bit

reference

address

from

the instruction.

If

indexing

is

also

specified,

the

Instruction

in

memory:

T~.~~"",,..":~~

..

~,......I

1-.

..

,......I....I~,..~~

'&"11_1111-11_.1

_0./1....,

.....

.."

_

.....

""'I....,~...,

generator:

Byte operation indexing alignment:

'

___

1

___

-

_I

IIIUCACU

not indexed

Halfword operation indexing alignment:

Word

operat!on indexing al ignment:

Shift operation indexing alignment:

Doubleword operation indexing alignment:

20-bit

effective

address:

appropriate

alignment

of

the

32-bit

contents

of

the

index

register

is

then made and the

addition

operation

performed.

The result

is

truncated

to the left of the

20-bit

operand

ob-

tained

from

the

indirect

address word.

In

real-extended

addressing,

20-bit

address

calculations

actually

encompass

22-,

21-,

20-,

and

19-bitcalculations,

respectively,

for

byte,

halfword, word, and doubleword

alignments (see Figures 8 and

9).

The

stack

pointer

doubleword for push-down instructions

contains a

20-bit

word address for the top

of

stack

address

field,

as shown in

the

following format:

I I

Figure

8.

Index Displacement Alignment (Real-Extended Addressing)

Main Memory 23

Loading...

Loading...