The new contents

of

the destination byte string

are:

# 6 1 2 . 5 0 0 # # # 1 2 . 3 4 f) # # 0 3 5

END

The new condition

code

is:

1011

The new contents

of

register 1

are:

X'xxx02013'

PUSH-DOWN

INSTRUCTIONS

(NON-PRIVILEGED)

The

term "push-down processing

ll

refers to the programming

technique

(used

extensively

in recursive routines)

of

storing

the

context

of

a

calculation

in memory, proceeding with a

new

set

of

information, and then

activating

the previously

stored information. Typically, this process involves a

re-

served

area

of

memory (stack) into which operands

are

pushed (stored) and from which operands

are

pulled

(loaded)

on a

last-in,

first-out

basis.

The

basic processor

pro-

vides for simplified and

efficient

programming

of

push-

down processing

by

means

of

the

following non-privi leged

instructions:

Instruction Name

Mnemonic

Push

Word

PSW

Pull Word

PLW

Push

Multiple

PSM

Pull

Multiple

PLM

Modify Stack Pointer

MSP

~T6r.1C

pmNTI=R

nnnRI

I=wnRn

I~PIl\

_

...

_

.....

_

........

_

....

-----_ .. _

.....

-

,---,

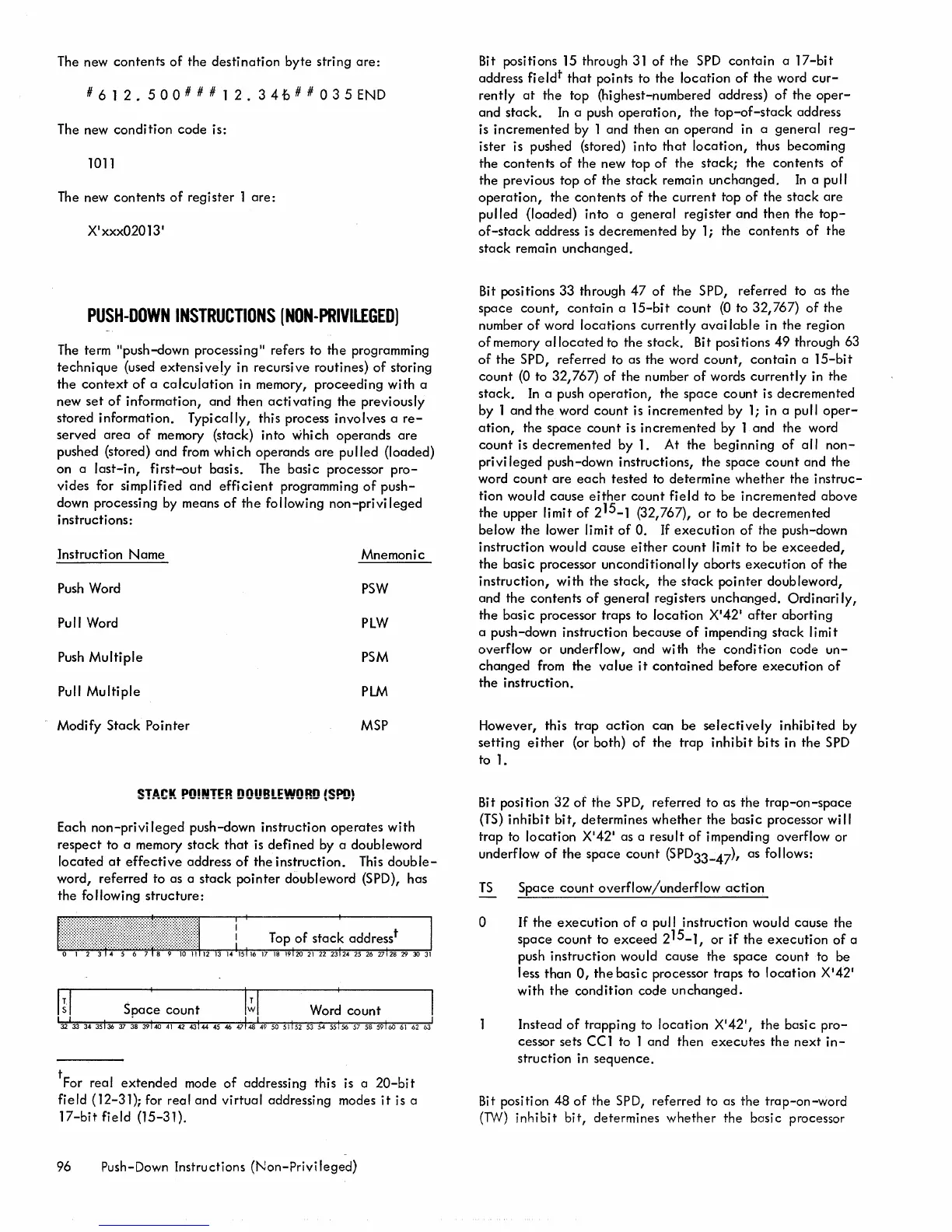

Each

non-privileged

push-down instruction

operates

with

respect to a memory stack

that

is

defined by a doubleword

located

at

effective

address

of

the instruction. This

double-

word, referred to as a

stack

pointer doubleword (SPD), has

the following structure:

I

~·I

Space

count

I~I

Word

count

I

'32 '33

34 35136

37

;8

39140

41

42

431«

45

46

47148

'49

50 5 d

52 53

54 55156

57

58 59160

61

62

63!

tFor real

extended

mode

of

addressing this is a

20-bit

field (12-31); for real and virtual addressing modes

it

is a

17-bit

field (15-31).

96 Push-Down Instructions

(Non-Privi leged)

Bit positions

15

through

31

of

the

SPD

contain

a

17-bit

address field

t

that

points to the location

of

the word

cur-

rently

at

the top (highest-numbered address)

of

the

oper-

and

stack.

In

a push

operation,

the

top-of-stack

address

is incremented by 1 and then an operand in a general

reg-

ister is pushed (stored) into

that

location,

thus becoming

the contents of the new top

of

the

stack;

the contents

of

the previous top

of

the stack remain unchanged.

In

a pull

operation,

the contents

of

the

current

top

of

the

stack

are

pulled

(loaded) into a general register and then the

top-

of-stack

address is decremented by

1;

the contents

of

the

stack

remain unchanged.

Bit positions 33 through

47

of

the SPD, referred to as the

space

count,

contain

a

15-bit

count

(0

to 32,767)

of

the

number

of

word locations currently

avai

lable in the region

of

memory

allocated

to the stack. Bit positions

49

through 63

of

the SPD, referred to as the word count,

contain

a

15-bit

count

(0

to 32,767) of the number

of

words

currently

in the

stack.

In

a push

operation,

the

space

count

is decremented

by 1 and the word

count

is incremented by

1;

in a pull

oper-

ation,

the

space

count is incremented by 1 and the word

count

is

decremented

by

1.

At the beginning

of

all

non-

privi leged push-down instructions, the space

count

and the

word

count

are

each

tested to determine

whether

the

instruc-

tion would cause

either

count

field

to be incremented above

the upper limit

of

2

15

_1

(32,767),

or

to be decremented

below the lower limit

of

O.

If

execution

of

the push-down

instruction would cause

either

count

limit to be

exceeded,

the basic processor unconditionally aborts

execution

of

the

instruction, with the

stack,

the

stack

pointer

doubleword,

and the contents

of

general registers unchanged. Ordinari Iy,

the basic processor traps to location

X'42'

after

aborting

a push-down instruction because

of

impending

stack

limit

overflow

or

underflow, and with the condition code

un-

changed

from the

value

it

contained

before

execution

of

the instruction.

However, this trap

action

can be

selectively

inhibited

by

setting

either

(or both)

of

the trap

inhibit

bits in the

SPD

to

1.

Bit position

32

of

the SPD, referred to as the

trap-on-space

(TS)

inhibit

bit,

determines

whether

the basic processor

wi

II

trap to location

X'42'

as a result

of

impending overflow or

underflow

of

the

space

count (SPD33-47)' as follows:

TS

Space

count

overflow/underflow

action

o

If the

execution

of

a pull instruction would cause the

space

count

to

exceed

2

15

_1, or if

the

execution

of

a

push instruction would cause the

space

count to be

less than

0,

the

basic processor traps to location

X'42'

with the condition code

unchanged.

Instead

of

trapping to location

X'42',

the basic

pro-

cessor sets CCl to 1 and then

executes

the

next

in-

struction in sequence.

Bit position 48

of

the SPD, referred to as the

trap-on-word

('f\N)

inhibit

bit,

determines

whether

the basic processor

Loading...

Loading...